**NORME

INTERNATIONALE

INTERNATIONAL

STANDARD**

**CEI

IEC

61340-3-1**

Première édition

First edition

2002-03

**Electrostatique –**

**Partie 3-1:

Méthodes pour la simulation

des effets électrostatiques –

Modèle du corps humain (HBM) –

Essais des composants**

**Electrostatics –**

**Part 3-1:

Methods for simulation of

electrostatic effects –

Human body model (HBM) –

Component testing**

Numéro de référence

Reference number

CEI/IEC 61340-3-1:2002

## Numérotation des publications

Depuis le 1er janvier 1997, les publications de la CEI sont numérotées à partir de 60000. Ainsi, la CEI 34-1 devient la CEI 60034-1.

## Editions consolidées

Les versions consolidées de certaines publications de la CEI incorporant les amendements sont disponibles. Par exemple, les numéros d'édition 1.0, 1.1 et 1.2 indiquent respectivement la publication de base, la publication de base incorporant l'amendement 1, et la publication de base incorporant les amendements 1 et 2.

## Informations supplémentaires sur les publications de la CEI

Le contenu technique des publications de la CEI est constamment revu par la CEI afin qu'il reflète l'état actuel de la technique. Des renseignements relatifs à cette publication, y compris sa validité, sont disponibles dans le Catalogue des publications de la CEI (voir ci-dessous) en plus des nouvelles éditions, amendements et corrigenda. Des informations sur les sujets à l'étude et l'avancement des travaux entrepris par le comité d'études qui a élaboré cette publication, ainsi que la liste des publications parues, sont également disponibles par l'intermédiaire de:

- **Site web de la CEI ([www.iec.ch](http://www.iec.ch))**

- **Catalogue des publications de la CEI**

Le catalogue en ligne sur le site web de la CEI ([www.iec.ch/catlg-f.htm](http://www.iec.ch/catlg-f.htm)) vous permet de faire des recherches en utilisant de nombreux critères, comprenant des recherches textuelles, par comité d'études ou date de publication. Des informations en ligne sont également disponibles sur les nouvelles publications, les publications remplaçées ou retirées, ainsi que sur les corrigenda.

- **IEC Just Published**

Ce résumé des dernières publications parues ([www.iec.ch/JP.htm](http://www.iec.ch/JP.htm)) est aussi disponible par courrier électronique. Veuillez prendre contact avec le Service client (voir ci-dessous) pour plus d'informations.

- **Service clients**

Si vous avez des questions au sujet de cette publication ou avez besoin de renseignements supplémentaires, prenez contact avec le Service clients.

Email: [custserv@iec.ch](mailto:custserv@iec.ch)

Tél: +41 22 919 02 11

Fax: +41 22 919 03 00

## Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

## Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

## Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC Catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- **IEC Web Site ([www.iec.ch](http://www.iec.ch))**

- **Catalogue of IEC publications**

The on-line catalogue on the IEC web site ([www.iec.ch/catlg-e.htm](http://www.iec.ch/catlg-e.htm)) enables you to search by a variety of criteria including text searches, technical committees and date of publication. Online information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

- **IEC Just Published**

This summary of recently issued publications ([www.iec.ch/JP.htm](http://www.iec.ch/JP.htm)) is also available by email. Please contact the Customer Service Centre (see below) for further information.

- **Customer Service Centre**

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: [custserv@iec.ch](mailto:custserv@iec.ch)

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI

IEC

61340-3-1

Première édition

First edition

2002-03

**Electrostatique –**

**Partie 3-1:

Méthodes pour la simulation

des effets électrostatiques –

Modèle du corps humain (HBM) –

Essais des composants**

**Electrostatics –**

**Part 3-1:

Methods for simulation of

electrostatic effects –

Human body model (HBM) –

Component testing**

© IEC 2002 Droits de reproduction réservés — Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'éditeur.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: [inmail@iec.ch](mailto:inmail@iec.ch) Web: [www.iec.ch](http://www.iec.ch)

Commission Electrotechnique Internationale

International Electrotechnical Commission

Международная Электротехническая Комиссия

CODE PRIX

PRICE CODE

K

*Pour prix, voir catalogue en vigueur

For price, see current catalogue*

## COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

## ÉLECTROSTATIQUE –

**Partie 3-1: Méthodes pour la simulation des effets électrostatiques –

Modèle du corps humain (HBM) – Essais des composants**

## AVANT-PROPOS

- 1) La CEI (Commission Électrotechnique Internationale) est une organisation mondiale de normalisation composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales. Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

- 2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure du possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés sont représentés dans chaque comité d'études.

- 3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés comme normes, spécifications techniques, rapports techniques ou guides et agréés comme tels par les Comités nationaux.

- 4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale correspondante doit être indiquée en termes clairs dans cette dernière.

- 5) La CEI n'a fixé aucune procédure concernant le marquage comme indication d'approbation et sa responsabilité n'est pas engagée quand un matériel est déclaré conforme à l'une de ses normes.

- 6) L'attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire l'objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 61340-3-1 a été établie par le comité d'études 101 de la CEI: Electrostatique.

Le texte de cette norme est issu des documents suivants:

| FDIS         | Rapport de vote |

|--------------|-----------------|

| 101/131/FDIS | 101/136/RVD     |

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant abouti à l'approbation de cette norme.

Cette publication a été rédigée selon les Directives ISO/CEI, Partie 3.

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant 2007. A cette date, la publication sera

- reconduite;

- supprimée;

- remplacée par une édition révisée, ou

- amendée.

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

## ELECTROSTATICS –

**Part 3-1: Methods for simulation of electrostatic effects –

Human body model (HBM) – Component testing**

## FOREWORD

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical specifications, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61340-3-1 has been prepared by IEC technical committee 101: Electrostatics.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 101/131/FDIS | 101/136/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 3.

The committee has decided that the contents of this publication will remain unchanged until 2007. At this date, the publication will be

- reconfirmed;

- withdrawn;

- replaced by a revised edition, or

- amended.

## INTRODUCTION

Les décharges électrostatiques se produisent fréquemment dans l'environnement. Les modèles équivalents électriques et électroniques sont utilisés pour simuler les décharges électrostatiques d'une manière contrôlée pour permettre les études et la prédition de dangers ou de dommages. Un des événements électrostatiques majeurs et largement reconnus est l'impulsion de décharge de courant transitoire provenant du bout des doigts humains à travers un objet à la terre. Ce type de modèle de décharge est désigné à juste titre comme «modèle du corps humain» (HBM). La présente norme fournit une description de la version moderne du HBM.

IECNORM.COM. Click to view the full PDF of IEC 61340-3-1:2002

## INTRODUCTION

Electrostatic discharges occur frequently in the environment. Electrical and electronic equivalent models are used to simulate electrostatic discharges in a controlled manner to allow study and prediction of hazards or damage. One of the most important and widely recognized electrostatic events is the transient current discharge pulse from a human body finger-tip through a grounded object. This type of discharge model is appropriately called the human body model (HBM). This standard provides a description of the modern version of the HBM.

IECNORM.COM. Click to view the full PDF of IEC 61340-3-1:2002

## ÉLECTROSTATIQUE –

### Partie 3-1: Méthodes pour la simulation des effets électrostatiques – Modèle du corps humain (HBM) – Essais des composants

#### 1 Domaine d'application

La présente partie de la CEI 61340 décrit les formes d'onde de courant de décharge utilisées pour définir le HBM et les prescriptions concernant les appareils de base utilisés pour développer ces formes d'onde. Les paramètres d'essai sont définis pour les essais et la classification de la sensibilité des décharges électrostatiques (ESD) des dispositifs de faible puissance au HBM.

L'objet de cette norme est d'établir un modèle d'essai qui reproduit des défaillances du HBM et définit la forme de la décharge de courant transitoire du HBM et tous les paramètres d'essai nécessaires pour assurer des résultats d'essai fiables et reproductibles. Les données reproductibles permettent des comparaisons précises des niveaux de sensibilité des décharges électrostatiques (ESD) du HBM.

#### 2 Définitions

Pour les besoins de la présente partie de la CEI 61340, les définitions suivantes sont applicables.

##### 2.1 **composant**

partie telle que la résistance, la diode, le transistor, le circuit intégré ou le circuit hybride

##### 2.2 **défaillance du composant**

état dans lequel un composant ne répond pas aux paramètres d'un ou de plusieurs paramètres techniques statiques ou dynamiques spécifiés

##### 2.3 **fenêtre de défaut du composant**

composant qui échoue dans une plage de basse tension mais réussit à un niveau de contrainte supérieur

NOTE Par exemple, un composant peut échouer à 500 V mais il réussit à 1 000 V.

##### 2.4 **paramètres techniques**

données de performances de composants statiques et dynamiques fournies par le fabricant ou l'utilisateur du composant

##### 2.5 **tension de tenue de l'ESD**

niveau maximal de l'ESD ne provoquant pas de défaillance de composant

## ELECTROSTATICS –

### Part 3-1: Methods for simulation of electrostatic effects – Human body model (HBM) – Component testing

#### 1 Scope

This part of IEC 61340 describes the discharge current waveforms used to define the HBM and the basic equipment requirements used to develop these waveforms. Test parameters are defined for testing and classifying the electrostatic discharge (ESD) sensitivity of non-powered devices to the HBM.

The purpose of this standard is to establish a test model that will replicate HBM failures and will define the HBM transient current discharge waveform and all necessary test parameters to ensure reliable, reproducible test results. Reproducible data will allow accurate comparisons of HBM ESD sensitivity levels.

#### 2 Definitions

For the purpose of this part of IEC 61340, the following definitions apply.

##### 2.1

##### **component**

part such as resistor, diode, transistor, integrated circuit or hybrid circuit

##### 2.2

##### **component failure**

condition in which a component does not meet one or more specified static or dynamic data sheet parameters

##### 2.3

##### **component fail window**

component fails in a low voltage range but passes at a higher stress level

NOTE For example, a component may fail at 500 V but passes at 1 000 V.

##### 2.4

##### **data sheet parameters**

static and dynamic component performance data supplied by the component manufacturer or user

##### 2.5

##### **ESD withstand voltage**

maximum ESD level that does not cause component failure

### 3 Appareils

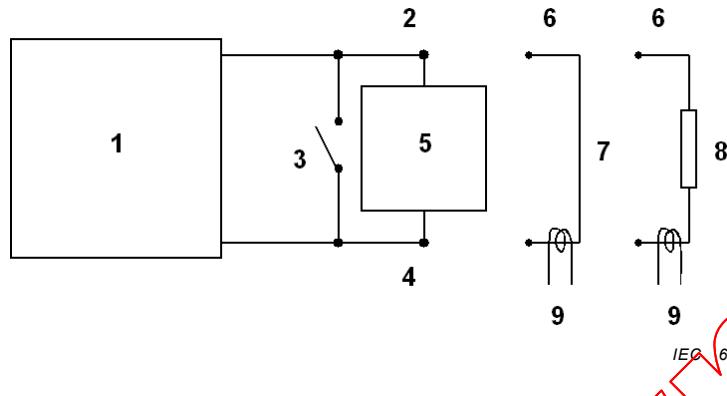

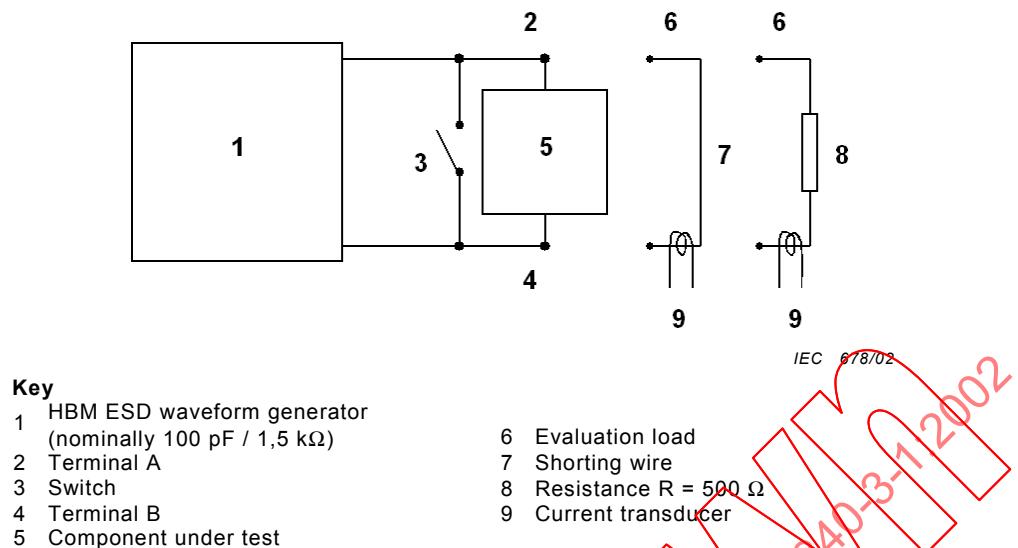

#### 3.1 Générateur de formes d'ESD du HBM

Cet appareil applique une impulsion de décharge de courant électrostatique du HBM à un composant à l'essai. Les charges d'évaluation de l'appareil d'essai et du circuit équivalent sont illustrées à la figure 1.

#### 3.2 Appareil de vérification de la forme d'onde

L'appareil capable de vérifier la forme d'onde de courant de l'HBM est défini dans la présente norme. Cet appareil comprend, entre autres, un système d'enregistrement de la forme d'onde, une résistance à haute tension et un transducteur de courant.

##### 3.2.1 Système d'enregistrement de la forme d'onde

Le système d'enregistrement de la forme d'onde doit avoir une largeur de bande à action unique minimale de 350 MHz.

##### 3.2.2 Charges d'évaluation

Deux charges d'évaluation sont nécessaires pour vérifier la fonctionnalité du générateur de formes d'onde:

- charge 1: un fil court-circuitant;

- charge 2: une résistance à inductance faible,  $500 \Omega \pm 1\%$ , 1 000 V.

La longueur du fil des charges d'évaluation (fil court-circuitant ou résistance) aussi courte que possible doit être compatible avec une connexion de la charge d'évaluation aux broches de référence appropriées (A et B à la figure 1) ou à toute autre broche lors du passage à travers le transducteur de courant.

##### 3.2.3 Transducteur de courant

Le transducteur de courant doit avoir une largeur de bande minimale de 350 MHz.

### 4 Prescriptions de forme d'onde de courant du HBM

#### 4.1 Généralités

Pour les essais de composants électroniques, la qualification du générateur de forme d'onde ESD du HBM doit assurer l'intégrité de la forme du courant de décharge à travers un fil court-circuitant et une charge résistive. Les prescriptions de la forme du fil court-circuitant sont spécifiées dans les figures 2a et 2b pour toutes les tensions positives et négatives définies dans le tableau 1, tandis que les prescriptions de forme de la charge résistive pour  $\pm 1\,000\text{ V}$  sont illustrées à la figure 3 et au tableau 1.

#### 4.2 Qualification et vérification de la forme d'onde

La qualification de l'appareil doit être réalisée au cours de l'essai de réception initial. La requalification est prescrite lorsque les réparations d'appareils sont effectuées en affectant éventuellement la forme d'onde. De plus, les formes d'onde doivent être vérifiées périodiquement. Il convient d'utiliser le tableau de dispositif d'essai pour comptage de broche le plus élevé. Dans le cas où la forme d'onde ne répondrait plus aux limites du tableau 1 et des figures 2a, 2b et 3, tous les essais ESD réalisés après la vérification satisfaisante précédente de la forme d'onde doivent être considérés comme non valables.

### 3 Equipment

#### 3.1 HBM ESD waveform generator

This equipment applies a HBM electrostatic current discharge pulse to a component under test. The equivalent circuit and tester evaluation loads are illustrated in figure 1.

#### 3.2 Waveform verification equipment

Equipment capable of verifying the HBM current waveform is defined in this standard. This equipment includes but is not limited to a waveform recording system, a high voltage resistor and a current transducer.

##### 3.2.1 Waveform recording system

The waveform recording system shall have a minimum single shot bandwidth of 350 MHz.

##### 3.2.2 Evaluation loads

Two evaluation loads are necessary to verify the functionality of the waveform generator:

- a) load 1: a shorting wire;

- b) load 2: a  $500 \Omega \pm 1\%$ , 1 000 V, low inductance resistor.

The lead length of the evaluation loads (shorting wire or resistor) shall be as short as possible consistent with connecting the evaluation load to the appropriate reference pins (A and B in figure 1) or to any other pins while passing through the current transducer.

##### 3.2.3 Current transducer

The current transducer shall have a minimum bandwidth of 350 MHz.

### 4 HBM current waveform requirements

#### 4.1 General

For electronic component testing, HBM ESD waveform generator qualification shall ensure waveform integrity of the discharge current through both a shorting wire and a resistive load. The shorting wire waveform requirements are specified in figures 2a and 2b for all positive and negative voltages defined in table 1, while the resistive load waveform requirements for  $\pm 1\,000\text{ V}$  are shown in figure 3 and table 1.

#### 4.2 Waveform qualification and verification

Equipment qualification shall be performed during initial acceptance testing. Re-qualification is required whenever equipment repairs are made that may affect the waveform. Additionally, the waveforms shall be verified periodically. The highest pin count test fixture board should be used. In case the waveform no longer meets the limits in table 1 and figures 2a, 2b and 3, all ESD testing performed after the previous satisfactory waveform check shall be considered invalid.

**Légende**

- 1 Générateur de forme d'onde ESD de l'HBM

(nominalement 100 pF / 1,5 kΩ)

2 Borne A

3 Interrupteur

4 Borne B

5 Composant à l'essai

- 6 Charge d'évaluation

7 Fil court-circuitant

8 Résistance R = 500 Ω

9 Transducteur de courant

**Figure 1 – Équivalent au générateur de forme d'onde ESD de l'HBM**

Prescriptions de la figure 1:

1. Les charges d'évaluation (7 et 8) sont spécifiées en 3.2.2.

2. Le transducteur de courant (9) est spécifié en 3.2.3.

3. L'inversion des bornes A(2) et B(4) pour réaliser une double polarité n'est pas autorisée.

4. L'interrupteur (3) est fermé de 10 ms à 100 ms après la période de livraison d'impulsions de chaque impulsion HBM pour s'assurer que le socle n'a pas été laissé dans un état chargé.

NOTE 1 La performance du générateur de forme d'onde est fortement influencée par l'inductance et la capacité parasites.

NOTE 2 Il faut prendre des précautions dans la conception du générateur de formes d'ondes pour éviter les transitoires de recharge et les impulsions doubles.

NOTE 3 Une résistance en série avec l'interrupteur assure une lente décharge du dispositif.

**Tableau 1 – Spécification de formes d'onde**

| Niveau | $I_{ps}$ courant de crête à travers un fil court-circuitant A | $I_{pr}$ courant de crête à travers une résistance de 500 Ω A | Tension équivalente V |

|--------|---------------------------------------------------------------|---------------------------------------------------------------|-----------------------|

| 1      | 0,17 ( $\pm 10\%$ )                                           |                                                               | 250                   |

| 2      | 0,33 ( $\pm 10\%$ )                                           |                                                               | 500                   |

| 3      | 0,67 ( $\pm 10\%$ )                                           | 0,375 – 0,550                                                 | 1 000                 |

| 4      | 1,33 ( $\pm 10\%$ )                                           |                                                               | 2 000                 |

| 5      | 2,67 ( $\pm 10\%$ )                                           |                                                               | 4 000                 |

| 6      | 5,33 ( $\pm 10\%$ )                                           |                                                               | 8 000                 |

**Figure 1 – HBM ESD waveform generator equivalent**

Requirements of figure 1:

1. The evaluation loads (7 and 8) are specified in 3.2.2.

2. The current transducer (9) is specified in 3.2.3.

3. The reversal of terminals A (2) and B (4) to achieve dual polarity is not permitted.

4. The switch (3) is closed 10 ms to 100 ms after the pulse delivery period of each single HBM pulse to ensure that the socket is not left in a charged state.

NOTE 1 The performance of the waveform generator is strongly influenced by parasitic capacitance and inductance.

NOTE 2 Precautions must be taken in the design of the waveform generator to avoid recharge transients and double pulses.

NOTE 3 A resistance in series with the switch ensures a slow discharge of the device.

**Table 1 – Waveform specification**

| Level | $I_{ps}$ peak current through a shorting wire<br>A | $I_{pr}$ peak current through a $500 \Omega$ resistor<br>A | Equivalent voltage<br>V |

|-------|----------------------------------------------------|------------------------------------------------------------|-------------------------|

| 1     | 0,17 ( $\pm 10 \%$ )                               |                                                            | 250                     |

| 2     | 0,33 ( $\pm 10 \%$ )                               |                                                            | 500                     |

| 3     | 0,67 ( $\pm 10 \%$ )                               | 0,375 – 0,550                                              | 1 000                   |

| 4     | 1,33 ( $\pm 10 \%$ )                               |                                                            | 2 000                   |

| 5     | 2,67 ( $\pm 10 \%$ )                               |                                                            | 4 000                   |

| 6     | 5,33 ( $\pm 10 \%$ )                               |                                                            | 8 000                   |

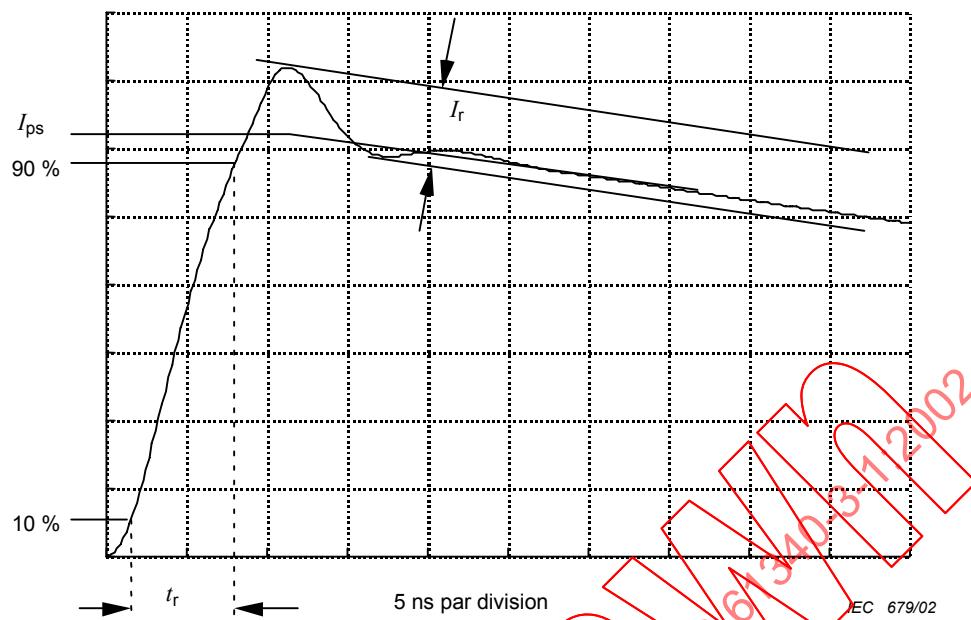

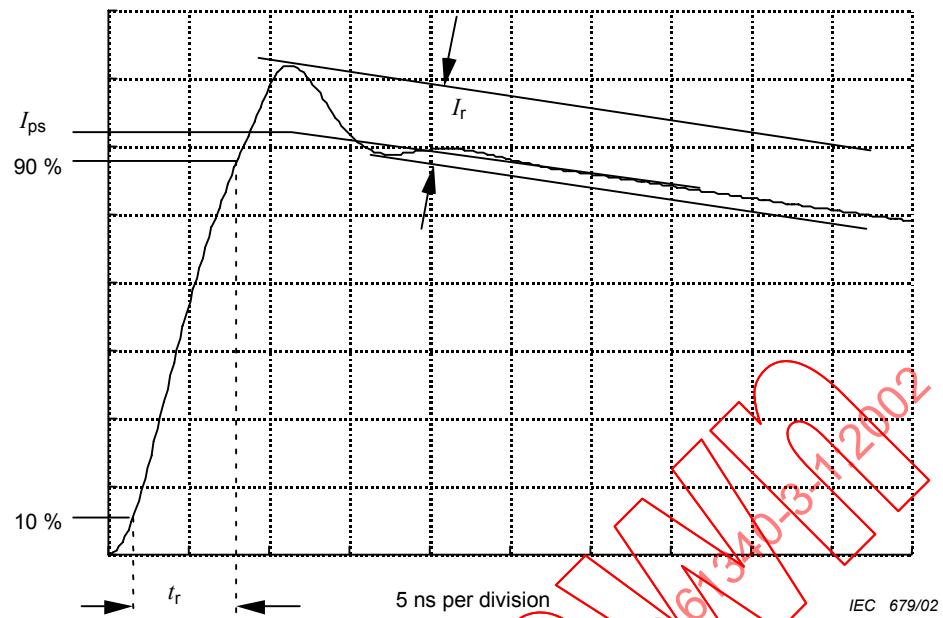

Figure 2a – Forme d'onde de courant type à travers un fil court-circuitant ( $t_r$ )

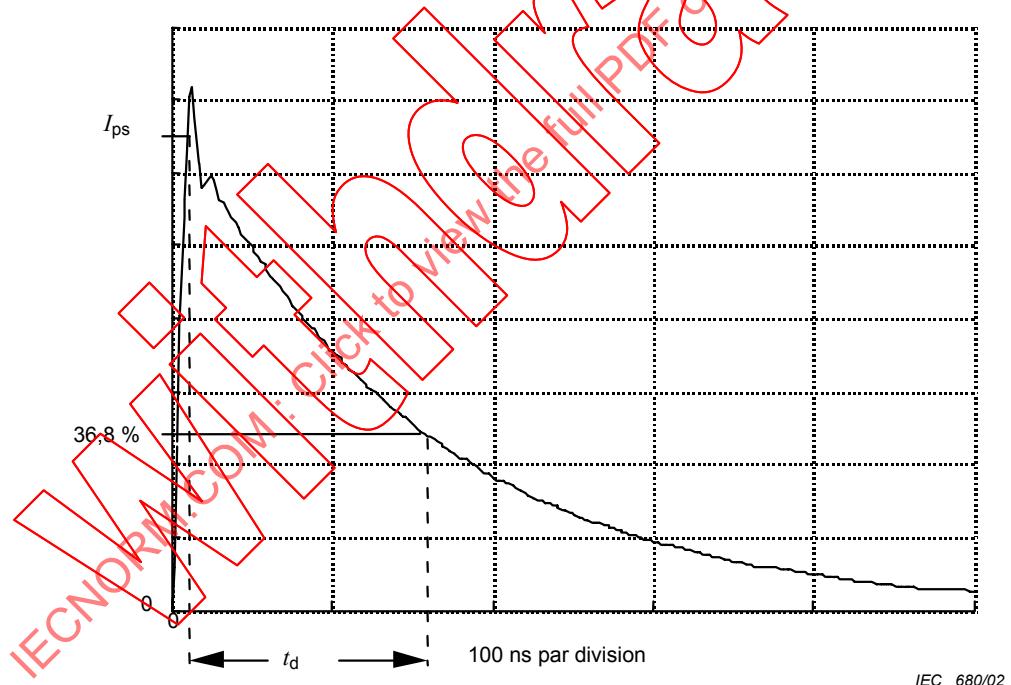

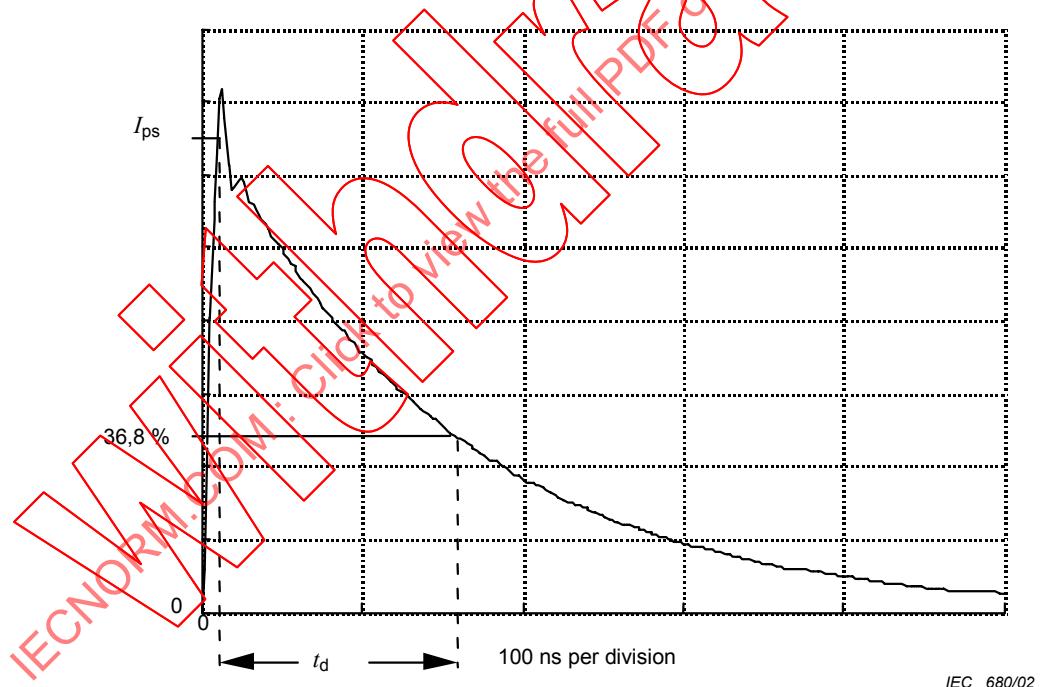

Figure 2b – Forme d'onde de courant type à travers un fil court-circuitant ( $t_d$ )

Prescriptions pour la figure 2:

L'impulsion de courant doit remplir les prescriptions suivantes:

$t_r$  temps de montée d'impulsion 2 ns à 10 ns;

$t_d$  temps d'extinction d'impulsion 150 ns  $\pm$  20 ns;

$I_r$  l'oscillation de crête à crête maximale autorisée doit être inférieure à 15 % de  $I_{ps}$ , lorsque la mesure est parallèle à la forme d'onde de courant, et que l'extinction ne présente aucune oscillation visible 100 ns après le début de l'impulsion.

Figure 2a – Typical current waveform through a shorting wire ( $t_r$ )

Figure 2b – Typical current waveform through a shorting wire ( $t_d$ )

Requirements for figure 2:

The current pulse shall meet the following requirements:

$t_r$  pulse rise time 2 ns to 10 ns;

$t_d$  pulse decay time 150 ns  $\pm$  20 ns;

$I_r$  the maximum allowed peak-to-peak ringing must be less than 15 % of  $I_{ps}$  when measured parallel to the current waveform, and decay with no observable ringing 100 ns after the start of the pulse.

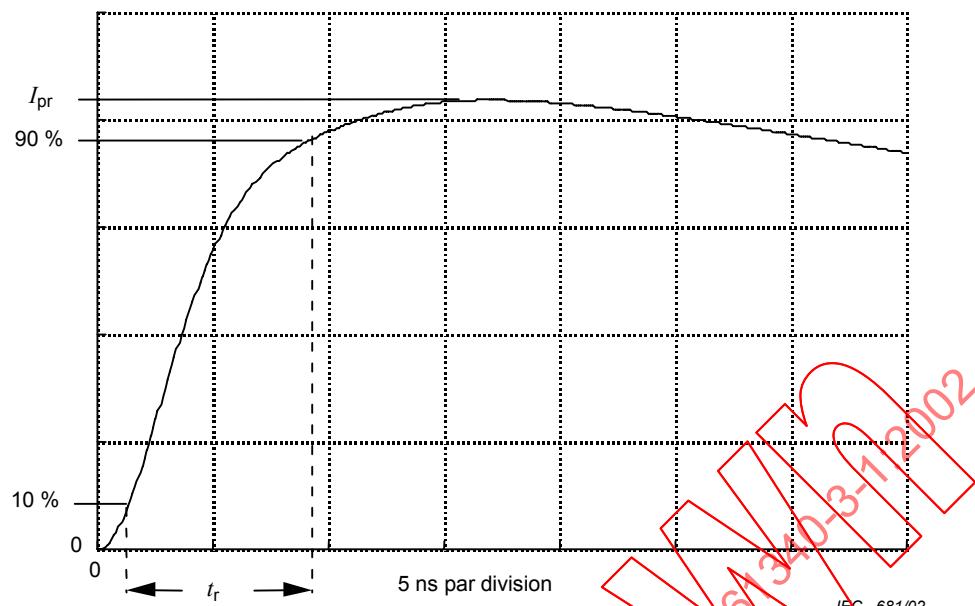

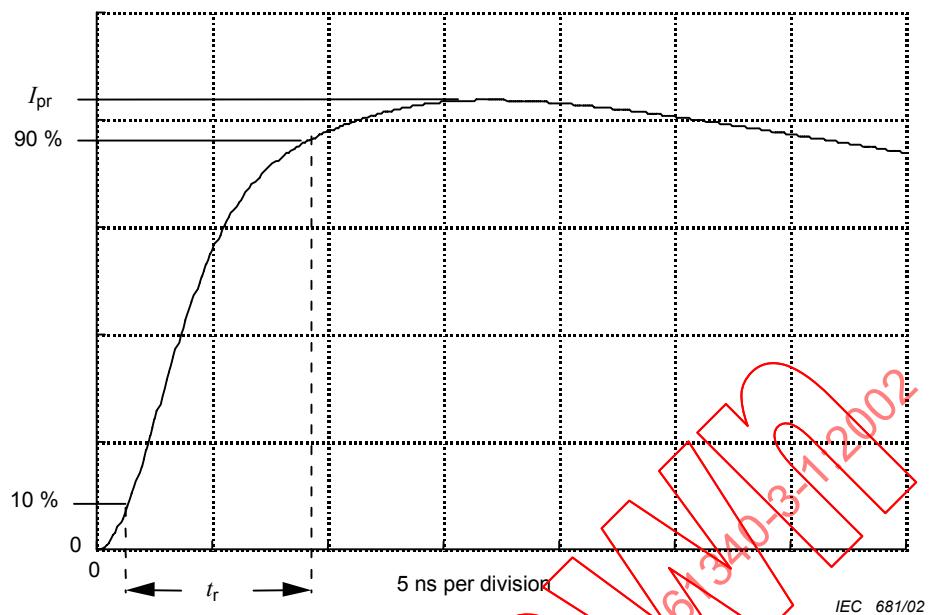

**Figure 3 – Forme d'onde de courant type à travers une résistance de 500  $\Omega$**

Prescriptions pour la figure 3:

L'impulsion de courant doit répondre aux caractéristiques suivantes:

$t_r$  temps de montée d'impulsion de 5 ns à 25 ns.

## 5 Paramètres d'essai

### 5.1 Combinaison de broches

#### 5.1.1 Circuits intégrés

Les combinaisons de broches à utiliser pour la contrainte ESD des composants de circuit intégré figurent dans le tableau 2. Le nombre réel des combinaisons de broches dépend du nombre de groupes de broches de terre ou d'alimentations.

$V_{ps(i)}$  au tableau 2 correspond à tout ensemble de broches appelées broches d'alimentation ou de terre (par exemple,  $V_{cc1}$ ,  $V_{cc2}$ ,  $V_{ss1}$ ,  $V_{ss2}$ , GND, etc.) qui sont raccordées métalliquement sur une puce ou à l'intérieur du boîtier. Les broches ainsi désignées qui sont raccordées résistivement ou isolées entre elles, sont considérées comme des ensembles séparés pour les besoins de ces essais.

Seules les broches qui fournissent du courant au composant doivent être considérées comme des broches d'alimentation,  $V_{ps}$ .

Toutes les autres broches (telles que des broches de sortie, d'entrée, d'adresse, de données,  $V_{ref}$ ,  $V_{pp}$ , des broches portant l'étiquette «pas de connexion (NC)», etc.), doivent être soumises à l'essai en tant que broches sans alimentation, non- $V_{ps}$ .

Figure 3 – Typical current waveform through a  $500 \Omega$  resistor

Requirements for figure 3:

The current pulse shall meet the following characteristics:

$t_r$  pulse rise time 5 ns to 25 ns.

## 5 Test parameters

### 5.1 Pin combinations

#### 5.1.1 Integrated circuits

The pin combinations to be used for ESD stressing of integrated circuit components are given in table 2. The actual number of pin combinations depends on the number of power supply or ground pin groups.

$V_{ps(i)}$  in table 2 is any set of like-named power supply or ground pins (e.g.,  $V_{cc1}$ ,  $V_{cc2}$ ,  $V_{ss1}$ ,  $V_{ss2}$ , GND, etc.) which are metallically connected on the chip or inside the package. Like-named pins that are resistively connected or isolated from each other are considered separate sets for the purpose of these tests.

Only those pins which supply current to the component shall be considered to be power supply pins,  $V_{ps}$ .

All other pins (e.g. output, input, address, data,  $V_{ref}$ ,  $V_{pp}$ , pins labelled “no connect (NC)”, etc.), shall be tested as non-power supply pins, non- $V_{ps}$ .

**Tableau 2 – Combinaisons de broches pour circuits intégrés**

| Ensemble de combinaisons de broches | Connecter individuellement à la borne A                                          | Connecter à la borne B (terre)                                              | Broches de flottement (non connectées)                     |

|-------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------|

| 1.1                                 | Toutes les broches une à la fois, sauf la ou les broches connectées à la borne B | $V_{ps}(1)$<br>(Premières broches d'alimentation ou de terre)               | Toutes les broches sauf la broche à l'essai et $V_{ps}(1)$ |

| 1.2                                 | Toutes les broches une à la fois, sauf la ou les broches connectées à la borne B | $V_{ps}(2)$<br>(Secondes broches d'alimentation ou de terre)                | Toutes les broches sauf la broche à l'essai et $V_{ps}(2)$ |

| 1.N                                 | Toutes les broches une à la fois, sauf la ou les broches connectées à la borne B | $V_{ps}(N)$<br>(Nièmes broches d'alimentation ou de terre)                  | Toutes les broches sauf la broche à l'essai et $V_{ps}(N)$ |

| 2                                   | Toutes les broches non- $V_{ps}$ , une à la fois                                 | Toutes autres broches non- $V_{ps}$ , sauf la broche connectée à la borne A | Toutes les broches $V_{ps}$                                |

### 5.1.2 Composants discrets

Des composants discrets (passifs et actifs) doivent être soumis à l'essai en utilisant toutes les combinaisons possibles de paires de broches (une broche raccordée à la borne A, une autre à la borne B) sans tenir compte de la fonction de broche.

### 5.2 Taille de l'échantillon

Au moins trois échantillons de composants.

### 5.3 Nombre d'impulsions

Une impulsion des deux polarités pour toutes les combinaisons de broches et les niveaux de contraintes.

### 5.4 Intervalle d'impulsions

L'intervalle le plus court entre les impulsions: 0,3 s.

## 6 Procédure d'essai

Un échantillon de composants doit être soumis à une contrainte à un niveau de tension pour toutes les combinaisons de broches.

Il est autorisé d'utiliser tout niveau de tension, en tant que niveau de contrainte de départ. (Pour éviter les fenêtres de défauts, il est recommandé de ne manquer aucun niveau de contrainte du tableau 1.)

Il est autorisé d'utiliser des échantillons séparés pour chaque combinaison de broches et/ou polarité.

Il est autorisé d'utiliser les mêmes échantillons au niveau de tension immédiatement supérieur si toutes les parties satisfont aux critères de défaillances.

Si un groupe différent d'échantillons est soumis à la contrainte HBM à chaque niveau et/ou combinaison de broches et/ou polarité, il est autorisé de réaliser les essais paramétriques et fonctionnels après avoir soumis à la contrainte HBM tous les groupes d'échantillons.

**Table 2 – Pin combinations for integrated circuits**

| Pin combination set | Connect individually to terminal A                                | Connect to terminal B (ground)                                       | Floating pins (unconnected)                    |

|---------------------|-------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------|

| 1.1                 | All pins one at a time, except the pin(s) connected to terminal B | $V_{ps}(1)$<br>(first power supply or ground pin(s))                 | All pins except pin under test and $V_{ps}(1)$ |

| 1.2                 | All pins one at a time, except the pin(s) connected to terminal B | $V_{ps}(2)$<br>(second power supply or ground pin(s))                | All pins except pin under test and $V_{ps}(2)$ |

| 1.N                 | All pins one at a time, except the pin(s) connected to terminal B | $V_{ps}(N)$<br>(Nth power supply or ground pin(s))                   | All pins except pin under test and $V_{ps}(N)$ |

| 2                   | All non- $V_{ps}$ pins one at a time                              | All other non- $V_{ps}$ pins, except the pin connected to terminal A | All $V_{ps}$ pins                              |

### 5.1.2 Discrete components

Discrete components (passive and active) shall be tested using all possible pin-pair combinations (one pin connected to terminal A, another to terminal B) regardless of pin function.

### 5.2 Sample size

At least three samples of components.

### 5.3 Pulse count

One pulse of both polarities for all pin combinations and stress levels.

### 5.4 Pulse interval

Shortest interval between pulses, 0.3 s.

## 6 Test procedure

A sample of components shall be stressed at one voltage level for all pin combinations.

It is permitted to use any voltage level as the starting stress level. (To avoid component fail windows, it is recommended not to miss any stress level of table 1.)

It is permitted to use separate samples for each pin combination and/or polarity.

It is permitted to use the same samples at the next higher voltage level if all parts pass the failure criteria.

If a different sample group is HBM stressed at each level and/or pin combination and/or polarity, it is permitted to perform the parametric and functional testing after all sample groups have been HBM stressed.

## 7 Critère de défaillance

Un composant est considéré comme ayant une défaillance ESD s'il ne répond pas à tous les paramètres techniques dynamiques et statiques spécifiés (données de performances de composants statiques et dynamiques fournies par le fabricant ou l'utilisateur).

Si des essais sont nécessaires à de multiples températures, les essais doivent être réalisés d'abord à la température la plus faible.

## 8 Classification

Les composants sont classés selon leur tension de tenue ESD (le niveau de contrainte HBM maximal qui ne provoque pas de défaillance du composant à condition que tous les composants soumis à la contrainte à des niveaux plus faibles aient également résisté). Les classes de sensibilité ESD du HBM sont fournies au tableau 3. Une classification plus fine peut être utilisée de manière facultative.

Tableau 3 – Classes de sensibilité ESD du HBM

| Classe | Plage de tensions |

|--------|-------------------|

| 0      | 0 à <250          |

| 1A     | 250 à <500        |

| 1B     | 500 à <1 000      |

| 1C     | 1 000 à <2 000    |

| 2      | 2 000 à <4 000    |

| 3      | ≥4 000            |

## 9 Remarque finale

Les essais de contrainte ESD doivent être considérés comme destructifs pour les composants, même s'ils n'échouent pas à l'essai.

## 7 Failure criteria

A component is considered to have an ESD failure if it does not meet all specified static and dynamic data sheet parameters (static and dynamic component performance data supplied by the component manufacturer or user).

If testing is required at multiple temperatures, testing shall be performed at the lowest temperature first.

## 8 Classification

The components are classified according to their ESD withstand voltage (maximum HBM stress level that does not cause component failure provided that all components stressed at lower levels have also passed). The HBM ESD sensitivity classes are given in table 3. A finer classification may optionally be used.

**Table 3 – HBM ESD sensitivity classes**

| Class | Voltage range<br>V |

|-------|--------------------|

| 0     | 0 to <250          |

| 1A    | 250 to <500        |

| 1B    | 500 to <1 000      |

| 1C    | 1 000 to <2 000    |

| 2     | 2 000 to <4 000    |

| 3     | ≥4 000             |

## 9 Final remark

ESD stress testing shall be considered destructive to the components, even if they did not fail during the test.

IECNORM.COM. Click to view the full PDF of IEC 61340-3-1:2002