Edition 1.0 2016-11

# **INTERNATIONAL** IEEE Std 2401™ **STANDARD**

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2015 IEEE

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Inc. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the IEEE. Enquiries about obtaining additional rights to this publication and other information requests should be addressed to the IEC or your local IEC member National Committee.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

info@iec.ch www.iec.ch Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue

New York, NY 10016-5997

United States of America

stds.info@ieee.org www.ieee.org

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

#### IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and iPad.

#### IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

#### IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and also once a month by email.

#### Electropedia www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing 20 000 terms and definitions in English and French, with equivalent terms in 15 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

#### YEC Glossary - std.iec.ch/glossary

65 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: csc@iec.ch.

Edition 1.0 2016-11

# **INTERNATIONAL** IEEE Std 2401™ **STANDARD**

Format for LSI-Package-Board interoperable design

**INTERNATIONAL ELECTROTECHNICAL** COMMISSION

ICS 31.180; 31.200; 35.060

ISBN 978-2-8322-3686-4

Warning! Make sure that you obtained this publication from an authorized distributor.

# **Contents**

| 1. Overview                                                                                                                                       |                                        |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|

| 1.1 Scope                                                                                                                                         |                                        | 1   |

| 1.2 Purpose                                                                                                                                       |                                        |     |

| 1.3 Key characteristics of the LSI-Package-Board Format                                                                                           |                                        |     |

| 1.4 Contents of this standard                                                                                                                     |                                        |     |

| 1. Contains of this surface                                                                                                                       |                                        |     |

| 2. Normative references                                                                                                                           |                                        | 3   |

| 2. 1 (01)11(01) (0 10) (01) (01)                                                                                                                  |                                        |     |

| 3. Definitions, acronyms, and abbreviations                                                                                                       |                                        | 3   |

| 3.1 Definitions                                                                                                                                   |                                        |     |

| 2.2 A granuma and abbraviations                                                                                                                   |                                        |     |

| 3.2 Acronyms and abbreviations                                                                                                                    | <i>જે</i>                              | 6   |

| A Consent of the LDD Formet                                                                                                                       | 20/1                                   |     |

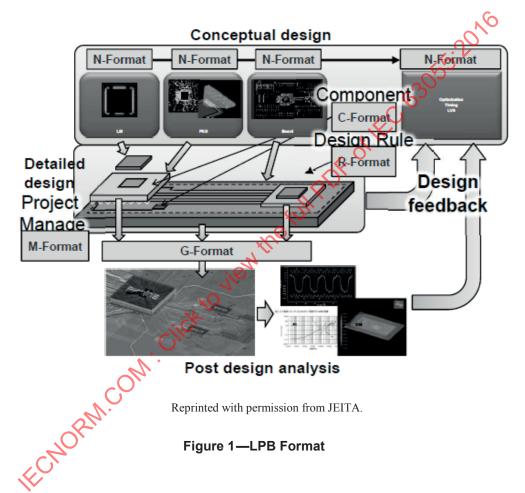

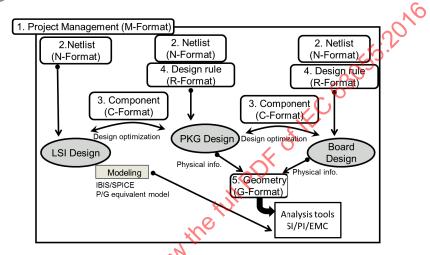

| 4. Concept of the LPB Format                                                                                                                      |                                        | 8   |

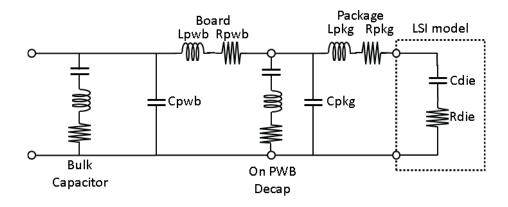

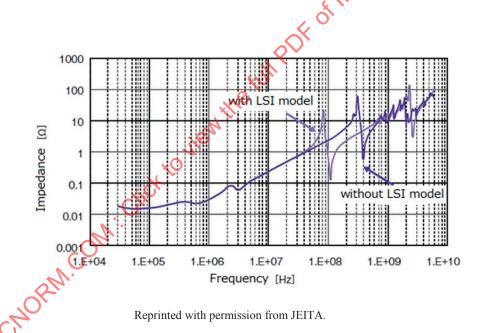

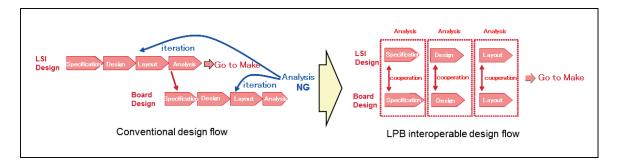

| 4.1 Technical background                                                                                                                          | ······································ | 8   |

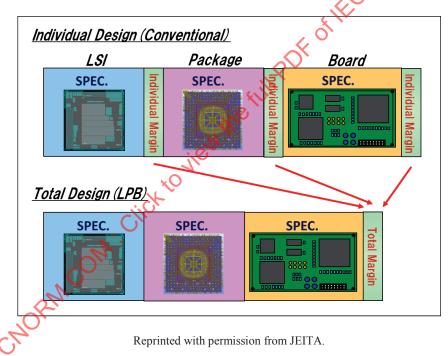

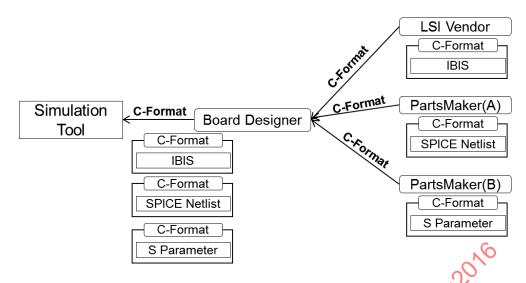

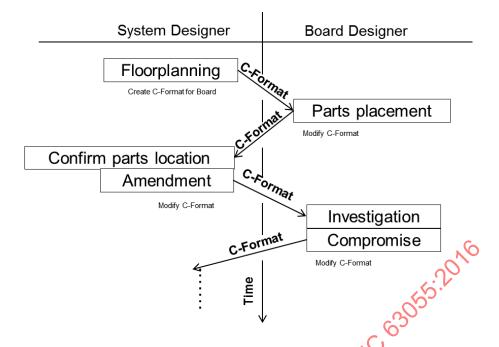

| 4.2 Conventional design                                                                                                                           |                                        | 8   |

| 4.3 Common problems at the design site                                                                                                            | <u>65</u>                              | 8   |

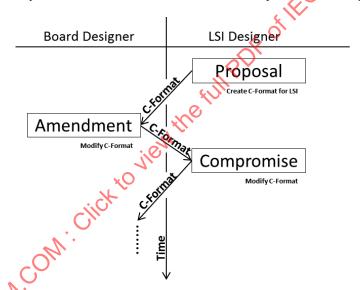

| 4.4 Concept of LPB interoperable design                                                                                                           | , V                                    | 9   |

| 4.1 Technical background                                                                                                                          | <u> </u>                               | 9   |

|                                                                                                                                                   |                                        |     |

| 4.7 Summary of LPB Format files                                                                                                                   | <u>;</u>                               | 10  |

| 4.7 Summary of LPB Format files                                                                                                                   | 4                                      |     |

| 5. Language basics                                                                                                                                | <u>)`</u>                              | 16  |

| , Y                                                                                                                                               | •                                      |     |

| 6 Common elements in M-Format C-Format and R-Format                                                                                               |                                        | 10  |

| 6 1 General                                                                                                                                       |                                        | 13  |

| 6.1 General                                                                                                                                       |                                        | 19  |

| 6.3 The <alahal> element</alahal>                                                                                                                 |                                        | 10  |

| 0.5 THE SHOURT CICINCIL                                                                                                                           |                                        | 15  |

| 6.3 The <global> element  7. M-Format  7.1 M-Format file structure  7.2 The <include> element  7.3 The <class> element</class></include></global> |                                        | 2.1 |

| /. M-Format.                                                                                                                                      |                                        | 3   |

| 7.1 M-Format file structure                                                                                                                       |                                        | 3   |

| 7.2 The <include> element</include>                                                                                                               |                                        | 31  |

| 7.3 The <class> element</class>                                                                                                                   |                                        | 32  |

|                                                                                                                                                   |                                        |     |

| 8. C-Format                                                                                                                                       |                                        |     |

| 8.1 C-Format file structure                                                                                                                       |                                        |     |

| 8.2 The <module> element</module>                                                                                                                 |                                        |     |

| 8.3 The <component> element</component>                                                                                                           |                                        | 82  |

|                                                                                                                                                   |                                        |     |

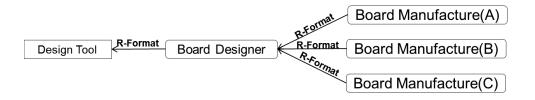

| 9. R-Format                                                                                                                                       |                                        | 86  |

| 9.1 R-Format file structure                                                                                                                       |                                        |     |

| 9.2 The Physicaldesign> element                                                                                                                   |                                        |     |

| 9.3 The <constraintrule> element</constraintrule>                                                                                                 |                                        |     |

| 7.5 The Constantitude Coment                                                                                                                      |                                        | 110 |

| 10 N Format                                                                                                                                       |                                        | 122 |

| 10. N-Format                                                                                                                                      |                                        |     |

| 10.1 Purpose of the N-Format file                                                                                                                 |                                        |     |

| 10.2 How to identify the power/ground network                                                                                                     |                                        |     |

| 10.3 Example                                                                                                                                      |                                        | 122 |

|                                                                                                                                                   |                                        |     |

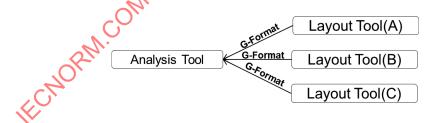

| 11. G-Format                                                                                                                                      |                                        |     |

| 11.1 Language basics of G-Format                                                                                                                  |                                        |     |

| 11.2 Structure                                                                                                                                    |                                        | 123 |

| 11.3 Header section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 124  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 11.4 Material section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12:  |

| 11.5 Layer section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120  |

| 11.6 Shape section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 11.7 Board geometry section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 11.8 Padstack section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 11.9 Part section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 11.10 Component section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 11.11 Net attribute section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 11.12 Netlist section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 11.13 Via section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

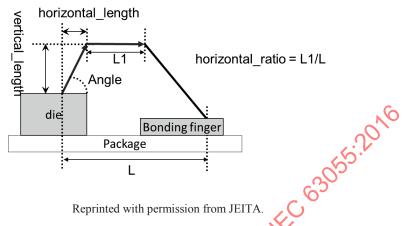

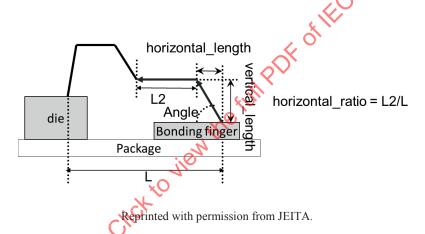

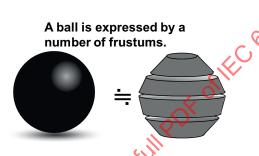

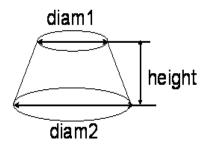

| 11.14 Bondwire section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 11.15 Route section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14   |

| A A (in Commercial) Diblication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.4. |

| Annex A (informative) Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 143  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NO   |

| Annex B (informative) Examples of utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 140  |

| Annex B (informative) Examples of utilization  B.1 Understanding the function of the LPB Format  B.2 Test bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| B.2 Test bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

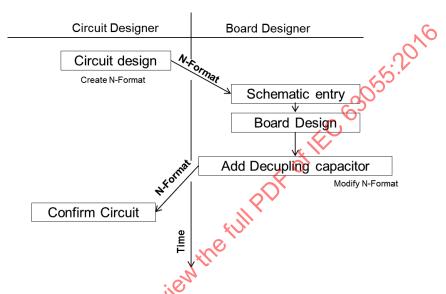

| B.3 Design flow example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 148  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| B.5 Simulations using the sample files in the LPB Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 182  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| Annex C (informative) XML Encryption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 184  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| Annex D (informative) MD5 checksum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18'  |

| Alliex B (Illiotinutive) WB3 Checksum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Annay E (informativa) Chin Dagkaga Interface Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100  |

| E 1 Conoral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100  |