# ISO/IEC 14165-151

Edition 1.0 2017-11

# **INTERNATIONAL STANDARD**

JaseT) FILL POLICY AND STANDARD SECONDARY OF THE STANDARD SECOND CHARLES OF THE STANDARD SECONDARY OF THE STANDARY OF THE STANDARD SECONDARY OF THE STANDARY OF THE STANDARD SECONDARY OF THE SECO colour

SO/IEC 14165-151:2017-11(en)

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2017 ISO/IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about ISO/IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IFC Central Office Tel: +41 22 919 02 11 3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch Switzerland www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

#### IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and

# IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

#### IEC Just Published - webstore.iec.ch/justpublished

sher and view circk to view standards is of the control of the con Stay up to date on all new IEC publications. Just Published

### Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing 20 000 terms and definitions in English and French, with equivalent terms in 16 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

# IEC Glossary - std iec.ch/glossary

65 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: csc@iec.ch.

Edition 1.0 2017-11

**ELECTROTECHNICAL** COMMISSION

ICS 35.200 ISBN 978-2-8322-5100-3

Warning! Make sure that you obtained this publication from an authorized distributor.

|                             |                  |                  |                    | 2011             |

|-----------------------------|------------------|------------------|--------------------|------------------|

| Information<br>Part 151: Ba | Technolo<br>aseT | ogy — Fibi       | re Channel –       | C 14165-151-2011 |

| Technologies de l'in        | formation — Fib  | ore Channel — Pa | artie 151 (FC-Base | Ç                |

|                             |                  |                  | III POF OT         |                  |

|                             |                  | ien the f        | 3.                 |                  |

|                             | cjick            | *10 No           |                    |                  |

|                             | COMI             |                  |                    |                  |

| SISO                        | •                |                  |                    |                  |

| ,OR                         |                  |                  |                    |                  |

| RA                          |                  |                  |                    |                  |

| Contents Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| FOREWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |

| 1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )                                              |

| 2 Normative references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )                                              |

| 3 Terms, definitions, abbreviations, symbols, and conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |

| 3.5.5 Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                              |

| 4 Structure and concepts 4.1 Overview 4.2 Relationship with other standards 4.3 FC-BaseT PHY logical model 4.4 FC-BaseT usage of XGMII 4.5 Operation of FC-BaseT 4.5.1 Overview 4.5.2 PCS overview 4.5.3 PMA overview 4.6 FC-BaseT service primitives and interfaces 4.6.1 Overview 4.6.2 PMA service interface 4.6.3 Management function interface 4.7 FC-BaseT Nomenclature  19  19  19  19  19  19  19  19  19  1                                                                                                                                                                                                                                                                                                                             | )<br> <br> 22<br> 33<br> 4<br> 55<br> 55<br> 1 |

| 5 Physical Coding Sublayer (PCS)       32         5.1 Overview       32         5.2 PCS reset function       32         5.3 PCS transmit function       33         5.3.1 Overview       33         5.3.2 36/33 transcoding       34         5.3.3 Error detecting code       36         5.3.4 PCS scrambling       37         5.3.5 Schläfli Lattice coding       39         5.3.6 Trellis coding       40         5.3.7 Generation of PMA training sequences       41         5.4 PCS receive function       42         5.4.1 Overview       42         5.4.2 Decoding       43         5.4.3 PCS descrambling       44         5.4.4 33/36 transcoding       45         5.4.5 PCS synchronization       46         5.5 State Diagrams       46 | 223334                                         |

| 6 P | MA Sublayer and Medium Dependent Interface                       | <br>48 |

|-----|------------------------------------------------------------------|--------|

|     | 5.1 PMA Overview                                                 |        |

| 6   | 5.2 PMA Functions                                                |        |

|     | 6.2.1 PMA Reset function                                         |        |

|     | 6.2.2 PMA Transmit function                                      |        |

|     | 6.2.3 PMA Receive Function                                       |        |

|     | 6.2.4 PHY Control Function                                       |        |

|     | 6.2.5 Link Monitor Function                                      |        |

|     | 6.2.6 Clock Recovery Function                                    |        |

| _   | 6.2.7 State Diagrams                                             |        |

| 6   | 6.3 PMA Electrical Specification                                 |        |

|     | 6.3.1 Isolation and EMC Requirements                             |        |

|     | 6.3.2 Test Modes                                                 | <br>56 |

|     | 6.3.3 Transmitter Electrical Specifications                      | <br>59 |

| _   | 6.3.4 Receiver Electrical Specifications                         | <br>64 |

| ь   | 6.4 MDI Specification.                                           | <br>99 |

|     | 6.4.1 Overview                                                   | <br>66 |

|     | 6.4.2 MDI Mechanical Specification                               | <br>66 |

|     | 6.4.3 Automatic MDI/MDI-X Configuration.                         | <br>67 |

|     | 6.4.4 MDI Electrical Specification                               | <br>67 |

| _   | 6.4.5 MDI Fault tolerance                                        | <br>67 |

| 6   | 5.5 Link Segment Characteristics                                 | <br>67 |

|     | 6.5.1 Overview                                                   |        |

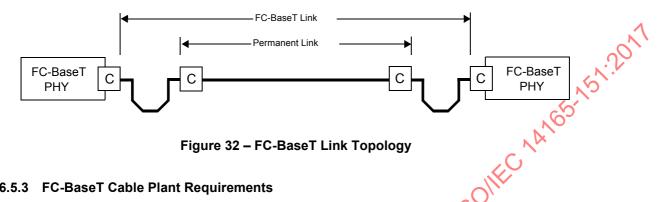

|     | 6.5.2 FC-BaseT Link Topology                                     | <br>68 |

|     | 6.5.3 FC-BaseT Cable Plant Requirements                          | <br>68 |

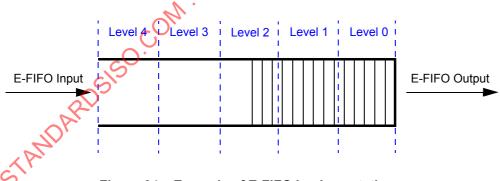

|     | Clasticity FIFO                                                  |        |

| / E | lasticity FIFO                                                   | <br>69 |

| 7   | '.1 Overview                                                     | <br>69 |

| 7   | 7.2 Ordered sets processing                                      | <br>70 |

| 7   | .3 Clock skew compensation                                       | <br>71 |

| ۰.  | HY startup procedure. 3.1 Overview 3.2 Host speeds determination | 70     |

| 8 P | HY startup procedure                                             | <br>73 |

| 8   | 3.1 Overview                                                     | <br>73 |

| 8   | 3.2 Host speeds determination                                    | <br>73 |

| 8   | 3.3 Host synchronization                                         | <br>73 |

| 8   | 8.4 FC-BaseT auto-negotiation                                    | <br>74 |

|     | 8.4.1 Overview                                                   | <br>74 |

|     | 8.4.2 FC-BaseT support.                                          |        |

|     | 8.4.3 Master-Slave relationship                                  |        |

|     | 8.4.4 Cable length estimation                                    |        |

|     | 8.4.5 Tentative Operating Speed Determination                    |        |

|     | 8.4.6 Configuration resolution                                   |        |

|     | 3.5 Speed downshift function                                     |        |

| 8   | 8.6 State diagrams                                               | <br>80 |

|     | $\mathcal{O}_{\mathbf{k}}$                                       |        |

|     | ort management                                                   |        |

| . , | .1 Overview                                                      |        |

|     | 0.2 FC-BaseT management registers                                |        |

|     | 0.3 Control Register                                             |        |

|     | 0.4 Status Register                                              |        |

|     | 0.5 Speed Downshift Register                                     |        |

|     | 0.6 Test Register                                                |        |

|     | 0.7 SNR Margin Registers                                         |        |

| 9   | 0.8 Auto-Negotiation Pages Registers                             | <br>95 |

| Annex A (informative) Additional 36/33 Mappings A.1 Overview. A.2 Notation A.3 Additional mappings. | 98<br>98 |

|-----------------------------------------------------------------------------------------------------|----------|

| Annex B (informative) Schläfli Lattice coding                                                       | 00       |

| Annex C (informative) Recommended 4GFC-BaseT power schedule                                         | 02       |

| Bibliography                                                                                        | 03       |

STANDARDS SO. COM. Click to view the full place of the control of

| Figure     |                                                                                                                                                                                | Page         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 1   | State diagram notation example                                                                                                                                                 |              |

| Figure 2   | FC-BaseT topology                                                                                                                                                              | 19           |

| Figure 3   | FC-BaseT relationship to the OSI Reference Model,                                                                                                                              |              |

|            | the Fibre Channel Levels, and the IEEE 802.3 LAN Model                                                                                                                         |              |

| Figure 4   | An FC-BaseT PHY logical model                                                                                                                                                  |              |

| Figure 5   | PCS and PMA functional block diagram                                                                                                                                           |              |

| Figure 6   | PCS and PMA service interfaces                                                                                                                                                 |              |

| Figure 7   | FC-BaseT nomenclature                                                                                                                                                          |              |

| Figure 8   | PCS reference diagram                                                                                                                                                          | 32           |

| Figure 9   | PCS transmit bit ordering                                                                                                                                                      |              |

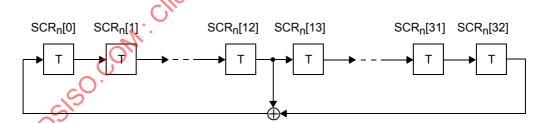

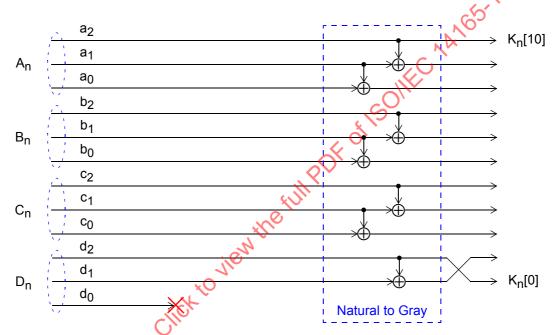

| Figure 10  |                                                                                                                                                                                | . 37         |

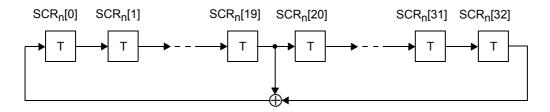

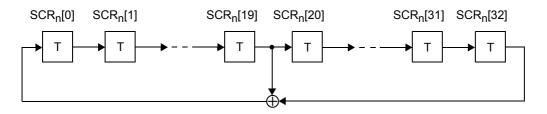

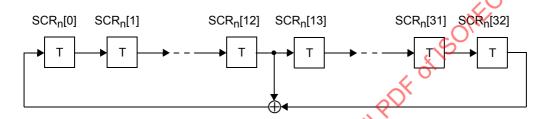

| Figure 11  | Side-stream scrambler for the Slave PHY                                                                                                                                        | . <b></b> 38 |

| Figure 12  | 4D PAM-8 Schläfli Lattice encoder                                                                                                                                              | 39           |

| Figure 13  | 4D PAM-8 Trellis encoder                                                                                                                                                       | 40           |

| Figure 14  | Generation of PMA training PAM-2 sequences                                                                                                                                     | 41           |

| Figure 15  | PCS receive bit ordering                                                                                                                                                       | 42           |

| Figure 16  | 4D PAM-8 Schläfli Lattice decoder                                                                                                                                              | 43           |

| Figure 17  | 4D PAM-8 Trellis encoder  Generation of PMA training PAM-2 sequences  PCS receive bit ordering  4D PAM-8 Schläfli Lattice decoder.  Side-stream descrambler for the Master PHY | 44           |

| Figure 18  | Side-stream descrambler for the Slave PHY                                                                                                                                      | 44           |

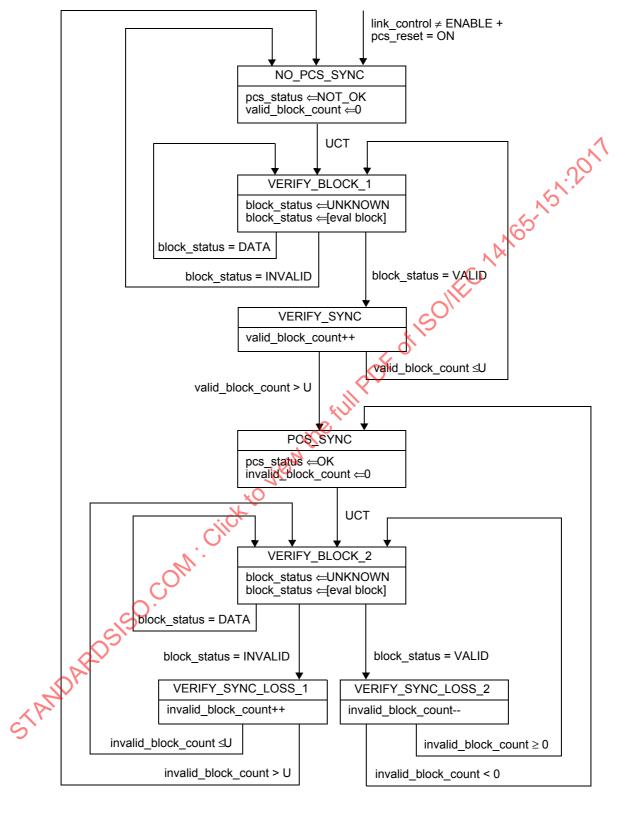

| Figure 19  | PCS synchronization state diagram                                                                                                                                              | 47           |

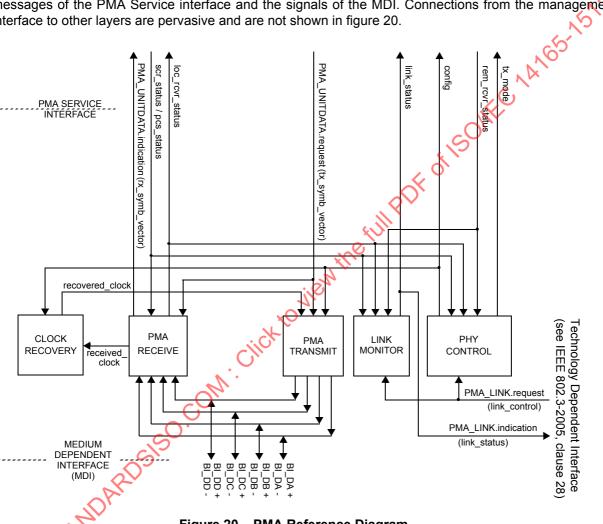

| Figure 20  | PMA Reference Diagram                                                                                                                                                          | 48           |

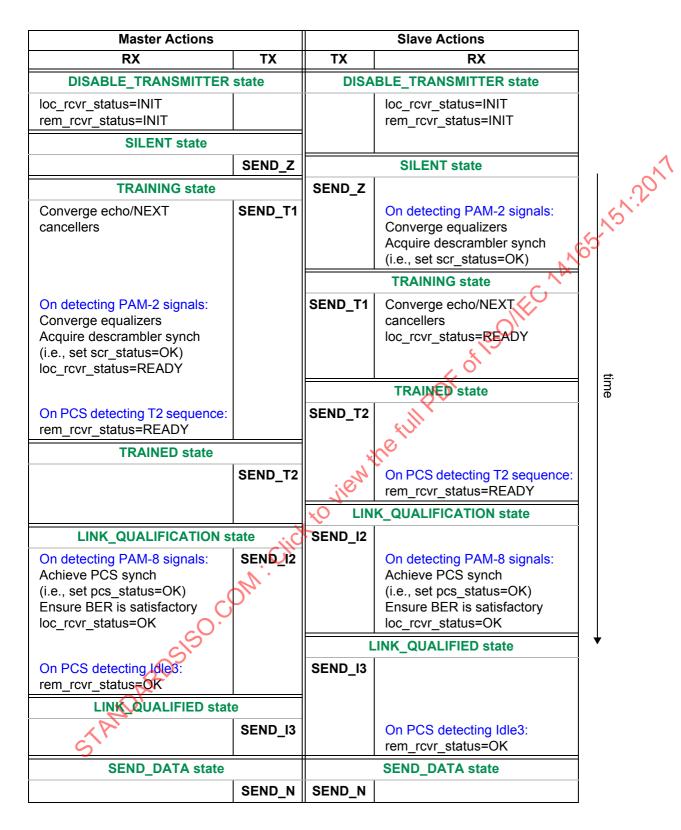

| Figure 21  | Example of Link Establishment                                                                                                                                                  | 52           |

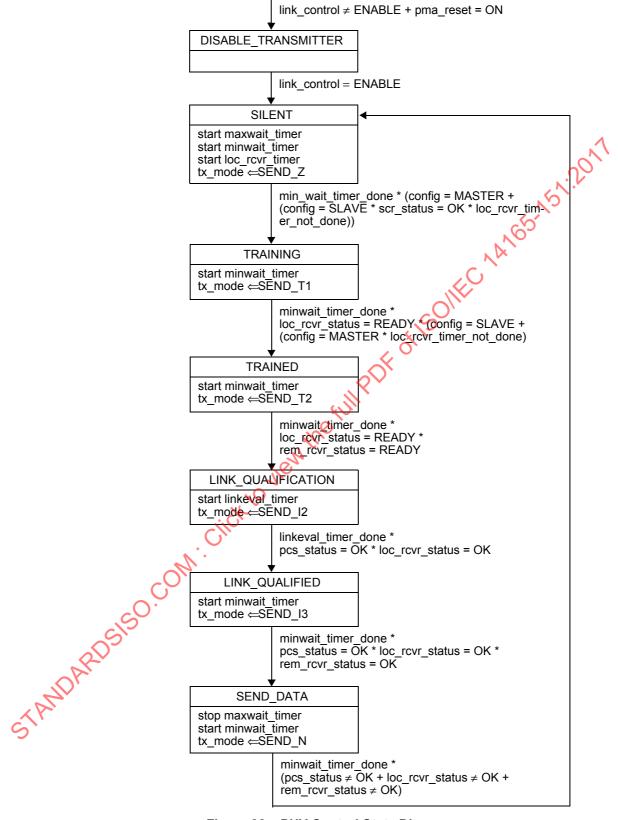

| Figure 22  | PHY Control State Diagram                                                                                                                                                      | 55           |

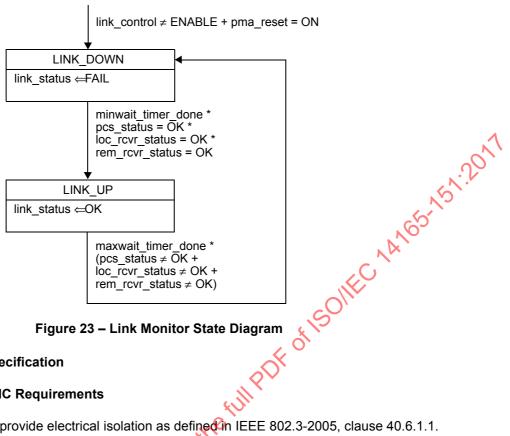

| Figure 23  | Link Monitor State Diagram                                                                                                                                                     | 56           |

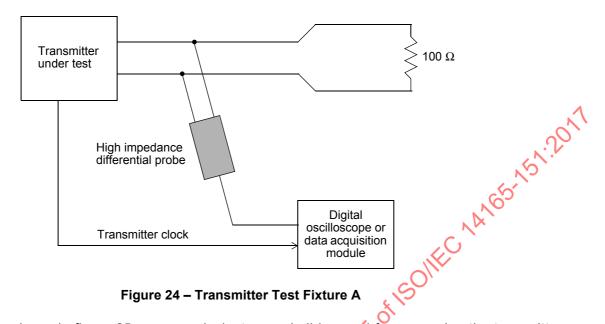

| Figure 24  | Transmitter Test Fixture A                                                                                                                                                     | 58           |

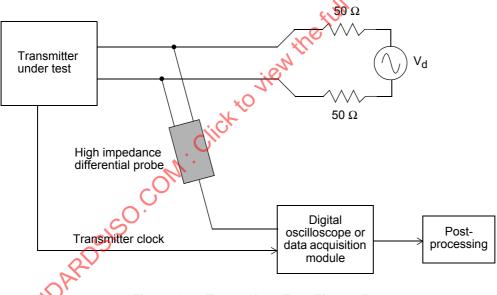

| Figure 25  |                                                                                                                                                                                | 58           |

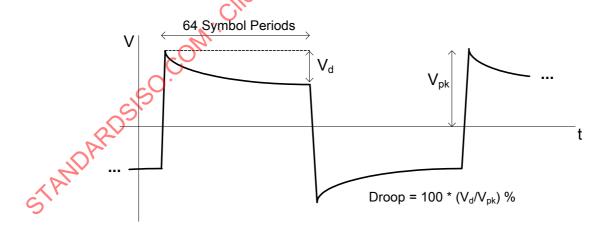

| Figure 26  | rest Mode i Output (not to scale)                                                                                                                                              | 59           |

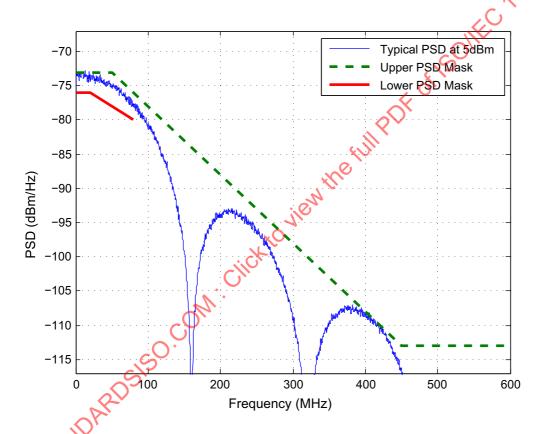

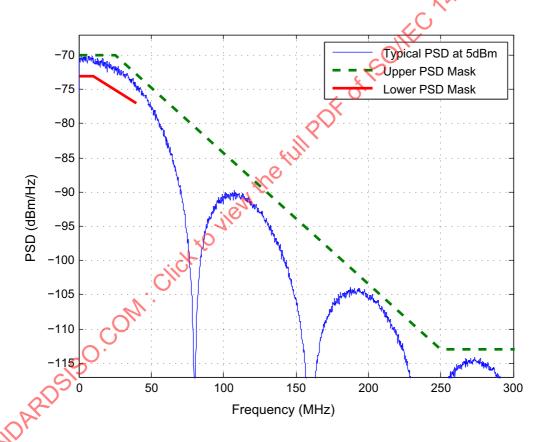

| Figure 27  |                                                                                                                                                                                |              |

| Figure 28  |                                                                                                                                                                                |              |

| Figure 29  |                                                                                                                                                                                |              |

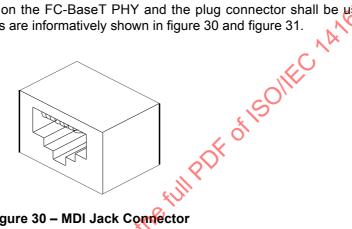

| Figure 30  |                                                                                                                                                                                |              |

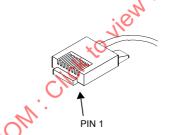

| Figure 31  | Balanced Cabling Plug Connector                                                                                                                                                |              |

| Figure 32  |                                                                                                                                                                                |              |

| Figure 33  |                                                                                                                                                                                |              |

| Figure 34  |                                                                                                                                                                                |              |

| Figure 35  |                                                                                                                                                                                |              |

| Figure 36  |                                                                                                                                                                                |              |

| Figure 37  |                                                                                                                                                                                |              |

| Figure 38  |                                                                                                                                                                                |              |

| Figure 39  | Clock loopback state diagram                                                                                                                                                   | 85           |

| Figure B 1 | 1C4D symbol error rate in function of SNR                                                                                                                                      | 100          |

| Table Page                                                                        |   |

|-----------------------------------------------------------------------------------|---|

| Table 1 ISO and American Conventions                                              |   |

| Table 2 State Diagram Operators                                                   |   |

| Table 3 FC-BaseT design goals for data rates and cable reaches                    |   |

| for the cabling channels specified by ISO/IEC 11801:2002/AMD2:2010                |   |

| Table 4 XGMII frequencies for FC-BaseT                                            |   |

| Table 5 XGMII characters                                                          |   |

| Table 6 FC-BaseT symbol and data rates                                            |   |

| Table 7 Fibre Channel words                                                       |   |

| Table 8 XGMII representation of Fibre Channel words                               |   |

| Table 9 36/33 transcoding                                                         |   |

| Table 10 36/33 transcoding examples                                               | 2 |

| Table 11 Bit to symbols mapping                                                   | ŀ |

| Table 12 PMA training sequences                                                   |   |

| Table 13 PCS synchronization state variables                                      |   |

| Table 14 Idle2 and Idle3 Ordered Sets                                             |   |

| Table 15 PHY Control and Link Monitor State Variables                             |   |

| Table 16 PHY Control and Link Monitor Timers                                      |   |

| Table 17 Management Register Settings for Test Modes                              |   |

| Table 18 Disturbing Signal Frequency                                              |   |

| Table 18 Disturbing Signal Frequency    59      Table 19 Droop Requirements    59 |   |

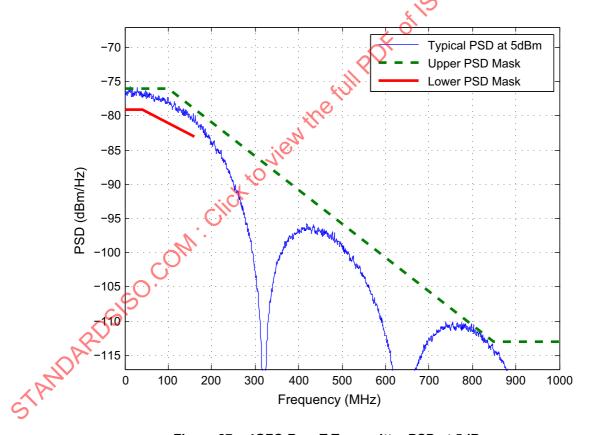

| Table 20 Transmitter Power Schedule                                               |   |

| Table 21 Transmitter Frequency Requirements 64                                    |   |

| Table 22 Receiver Frequency Requirements                                          |   |

| Table 23 Alien Noise Requirements                                                 |   |

| Table 24 Assignment of PMA Signals to MDI and MDI-X Contacts                      |   |

| Table 25 FC-base I Midi Electrical Regulrements                                   |   |

| Table 26 FC-BaseT Cable Plant Requirements                                        |   |

| Table 27 Extended Fill Words                                                      |   |

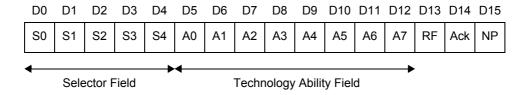

| Table 28 Technology Ability Field                                                 |   |

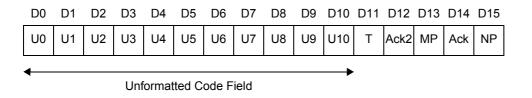

| Table 29 Unformatted code field of the first unformatted page                     |   |

| Table 30 Master-Slave seed assignment                                             |   |

| Table 31 Unformatted code field of the second unformatted page                    |   |

| Table 32 Unformatted code field of the third unformatted page                     |   |

| Table 33 Cable length estimation state variables                                  |   |

| Table 34 Cable length estimation timers                                           |   |

| Table 35 FC-BaseT registers                                                       |   |

| Table 36 FC-BaseT control register bits                                           |   |

| Table 37 FC-BaseT status register bits                                            |   |

| Table 38 FC-BaseT speed downshift register bits                                   |   |

| Table 39 FC-BaseT test register bits                                              |   |

| Table 40 FC-BaseT SNR margin registers bits                                       |   |

| Table 41 FC-BaseTauto-negotiation pages registers bits                            |   |

| Table A.1 Additional 36/33 mappings                                               |   |

| Table A.2 6-bit encoding of XGMII control characters                              |   |

| Table C.1 Recommended transmitter power schedule                                  |   |

# INFORMATION TECHNOLOGY – FIBRE CHANNEL –

Part 151: Fibre Channel BaseT (FC-BaseT)

## **FOREWORD**

- 1) ISO (International Organization for Standardization) and IEC (International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards. Their preparation is entrusted to technical committees; any ISO and IEC member body interested in the subject dealt with may participate in this preparatory work. International governmental and non-governmental organizations liaising with ISO and IEC also participate in this preparation.

- In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC

Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting. Publication as an International Standard requires approval by at least 75% of the national bodies casting a vote.

- 3) The formal decisions or agreements of IEC and ISO on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC and ISO member bodies.

- 4) IEC, ISO and ISO/IEC publications have the form of recommendations for international use and are accepted by IEC and ISO member bodies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC, ISO and ISO/IEC publications is accurate, IEC or ISO cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 5) In order to promote international uniformity, IEC and ISO member bodies undertake to apply IEC, ISO and ISO/IEC publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any ISO/IEC publication and the corresponding national or regional publication should be clearly indicated in the latter.

- 6) ISO and IEC provide no marking procedure to indicate their approval and cannot be rendered responsible for any equipment declared to be in conformity with an ISO/IEC publication.

- 7) All users should ensure that they have the latest edition of this publication.

- 8) No liability shall attach to IEC or ISO or its directors, employees, servants or agents including individual experts and members of their technical committees and IEC or ISO member bodies for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication of, use of, or reliance upon, this ISO/IEC publication or any other IEC, ISO or ISO/IEC publications.

- 9) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights.

International Standard ISO/IEC 14165-151 was prepared by subcommittee 25: Interconnection of information technology equipment, of ISO/IEC joint technical committee 1: Information technology.

The list of all currently available parts of the ISO/IEC 14165 series, under the general title *Information technology – Fibre Channel*, can be found on the IEC web site.

This International Standard has been approved by vote of the member bodies and the voting results may

be obtained from the address given on the second title page.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

IMPORTANT - The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

STANDARDS SO. COM. Click to view the full Politic lands of the Committee full Politic lands of the Com

# INTRODUCTION

This part of ISO/IEC 14165 describes extensions to the Fibre Channel signaling and physical layer requirements defined in ANSI INCITS 404-2005, Fibre Channel - Physical Interfaces 2, to transport Fibre Channel over the commonly available 4-pair balanced copper cablings specified in ISO/IEC 11801:2002 and TIA/EIA-568-B.2-2001. This document is one of the Fibre Channel family of standards.

STANDARDS SO. COM. Click to view the full Political Andrew the full Po

# INFORMATION TECHNOLOGY — FIBRE CHANNEL —

# Part 151: Fibre Channel BaseT (FC-BaseT)

# 1 Scope

This part of ISO/IEC 14165 describes extensions to the Fibre Channel signaling and physical layer requirements defined in ISO/IEC 14165-142, Fibre Channel - Physical Interfaces 2, to transport Fibre Channel over the commonly available 4-pair balanced copper cablings specified in ISO/IEC 11801:2002 and TIA/EIA-568-B.2-2001. This standard is one of the Fibre Channel family of standards.

### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

- IEC 60603-7-2, Connectors for electronic equipment Part 7-2: Detail specification for 8-way, unshielded, free and fixed connectors, for data transmissions with frequencies up to 100 MHz

- IEC 60603-7-3, Connectors for electronic equipment Part 7-3: Detail specification for 8-way, shielded, free and fixed connectors, for data transmission with frequencies up to 100 MHz

- IEC 60603-7-4, Connectors for electronic equipment Part 7-4: Detail specification for 8-way, unshielded, free and fixed connectors, for data transmissions with frequencies up to 250 MHz

- IEC 60603-7-5, Connectors for electronic equipment Part 7-5: Detail specification for 8-way, shielded, free and fixed connectors, for data transmissions with frequencies up to 250 MHz

ISO/IEC 14165-122, Information technology - Fibre Channel Part 122: Arbitrated Loop - 2 (FC-AL-2) [ANSI INCITS 332-1999 including ANSI INCITS 332-1999/AM1-2003 and ANSI INCITS 332-1999/AM2-2006]

ISO/IEC 11801:2002, Information technology - Generic cabling for customer premises

ISO/IEC 11801:2002/AMD1:2008

ISO/IEC 11801:2002/AMD2:2010

ISO/IEC TR 24750, Information technology - Assessment and mitigation of installed balanced cabling channels in order to support 10GBASE-T

ANSI INCITS 404-2006, Information technology - Fibre Channel - Part 142: Physical Interfaces - 2 (FC-PI-2)

ANSI INCITS 424-2007 Information technology - Fibre Channel - Framing and Signaling - 2 (FC-FS-2)

- IEEE Std 802.3-2005, Standard for information technology Telecommunications and information exchange between systems Local and metropolitan area networks Specific requirements Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications

- IEEE Std 802.3an-2006, Physical Layer and Management Parameters for 10 Gb/s Operation, Type 10GBASE-T

# 3 Terms, definitions, abbreviations, symbols, and conventions

### 3.1 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

#### 3.1.1

# 10 Gigabit Media Independent Interface

#### **XGMII**

interface defined in IEEE 802.3-2005 for 10 Gbit/s operations but used in this standard for lower speeds operations (see 4.4)

### 3.1.2

### **Auto-Negotiation**

algorithm that allows two devices at either end of a link segment to negotiate common data service functions

#### 3.1.3

#### balanced cable

cable consisting of one or more metallic symmetrical cable elements (e.g., twisted pairs)

### 3.1.4

# bit error rate

# **BER**

ratio of the number of bits received in error to the total number of bits received

## 3.1.5

#### dimension

component of the PHY that generates locally and recovers from the link partner a logical sequence of symbols

Note 1 to entry: A transmit or receive dimension is a logical reference for a wire pair, independent from the specific wire pair where symbols are sent or received.

Note 2 to entry: Dimensions A, B, C, and D are respectively associated with sequences  $A_n$ ,  $B_n$ ,  $C_n$ , and  $D_n$  (see 4.3).

# 3.1.6

# jitter

variations of signal transitions from their ideal positions in time. Jitter may be characterized by its spectral properties and its distribution in time

# 3.1.7

# link

transmission path between any two interfaces of generic cabling

#### 3.1.8

#### link segment

point-to-point full-duplex medium connection between two and only two Medium Dependent Interfaces (MDIs)

#### 3.1.9

### **Master PHY**

PHY that uses an external clock for generating its clock signals to determine the timing of transmitter and receiver operations

Note 1 to entry: It also uses the Master transmit scrambler generator polynomial for side-stream scrambling.

#### 3.1.10

## **Medium Dependent Interface**

#### MDI

mechanical and electrical interface between the transmission medium and the Physical Layer device

#### 3.1.11

#### **Ordered Set**

word composed of a special character in its first (left-most) position and data characters in its remaining positions (see FC-FS-2)

#### 3.1.12

# **Physical Coding Sublayer**

# PCS

portion of the Physical Layer that couples the XGMII and the Physical Medium Attachment (PMA)

Note 1 to entry: The PCS contains the functions to encode data bits for transmission via the PMA and to decode the received conditioned signal from the PMA.

#### 3.1.13

# **Physical Layer device**

#### **PHY**

portion of the Physical Layer between the Medium Dependent Interface (MDI) and the XGMII, consisting of the Physical Coding Sublayer (PCS) and the Physical Medium Attachment (PMA)

Note 1 to entry: The PHY contains the functions that transmit, receive, and manage the encoded signals that are impressed on and recovered from the physical medium.

# 3.1.14

# Physical Medium Attachment sublayer

## PMA sublayer

portion of the Physical Layer that contains the functions for transmission, reception, clock recovery and skew alignment

## 3.1.15

#### Scrambler

randomizing mechanism that is used to eliminate long strings of consecutive identical transmitted symbols and avoid the presence of spectral lines in the signal spectrum without changing the signaling rate

## 3.1.16

#### Side-stream scrambler

scrambler in which the state of the scrambler is dependent only on the prior state of the scrambler and not on the transmitted data

# 3.1.17

#### **Slave PHY**

PHY that recovers its clock from the received signal and uses it to determine the timing of transmitter operations

Note 1 to entry: It also uses the Slave transmit scrambler generator polynomial for side-stream scrambling.

### 3.1.18

# **Symbol**

smallest unit of data transmission on the medium

#### 3.1.19

# Symbol period

time interval for transmission of one symbol

# 3.1.20

sheath is online with the full part of the online of the o total number of symbols per second transferred to or from the Medium Dependent Interface (MDI) on a

#### 3.2 Editorial conventions

In this standard, a number of conditions, mechanisms, sequences, parameters, events, states, or similar terms are printed with the first letter of each word in uppercase and the rest lowercase (e.g., Exchange, Class). Any lowercase uses of these words have the normal technical English meanings.

Lists sequenced by letters (e.g., a-red, b-blue, c-green) show no ordering relationship between the listed items. Numbered lists (e.g., 1-red, 2-blue, 3-green) show an ordering relationship between the listed items.

The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a comma is used as the decimal point.) A comparison of the American and ISO conventions are shown 14165-151:201 in table 1.

ISO **American** 0,6 0.6 1 000 1,000 1 323 462.9 1.323.462.9

Table 1 - ISO and American Conventions

In case of any conflict between figure, table, and text, the text, then tables and finally figures take precedence.

In all of the figures, tables, and text of this document, the most significant bit of a binary quantity is shown on the left side.

When the value of a bit or field is not relevant, x or xx appears in place of a specific value.

Unless stated otherwise, numbers that are not immediately followed by lower-case b or h are decimal values, numbers immediately followed by lower-case b (xxb) are binary values, and numbers or upper case letters immediately followed by lower-case h (xxh) are hexadecimal values.

A numeric range is indicated by listing the two extremes separated by ".." (e.g., "1 .. 6" indicates the range from 1 to 6, including 1 and 6).

# 3.3 Abbreviations, acronyms, and symbols

Abbreviations, acronyms, and symbols applicable to this standard are listed. Definitions of several of these items are included in 3.1.

$\oplus$ The XOR operator

concatenation symbol (e.g., A | B represents the concatenation of A and B)  $\parallel$

4D 4-dimensional **BER** bit error rate Decibel dB E-FIFO Elasticity FIFO **EDC**

**Error Detecting Code** EIA **Electronic Industries Association EMC**

Electromagnetic Compatibility Electromagnetic Interference EMI

Far-end crosstalk **FEXT FLP** Fast Link Pulse

I2C Inter-Integrated Circuit bus **IEC** International Electrotechnical Commission **IEEE** Institute of Electrical and Electronics Engineers ISO International Organization for Standardization

LAN Local Area Network

MDI Medium Dependent Interface

**MDIO** Management Data Input/Output Interface

Media Independent Interface MII

**NEXT** Near-end crosstalk **NLP** Normal Link Pulse

OSI **Open Systems Interconnection** PAM Pulse Amplitude Modulation

- PAM Pulse Amplitude Modulation

PAM-2 2-level Pulse Amplitude Modulation

PAM-8 8-level Pulse Amplitude Modulation

PCS Physical Coding Sublayer

PHY Physical Layer device

PMA Physical Medium Attachment

ppm Parts per million

PSD Power Spectral Density

RF Remote Fault

RX Receiver

SNR Signal to Noise Ratio

TIA Telecommunication Industries Association

TX Transmitter

XGMII 10 Gigabit Media Independent Interface

3.4 Keywords

3.4 Keywords

3.4.1 expected: A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented. models assumed by this standard. Other hardware and software design models may also be implemented.

- **3.4.2** ignored: A keyword used to describe an unused bit, byte, word, field or code value. The contents or value of an ignored bit, byte, word, field or code value shall not be examined by the receiving device and may be set to any value by the transmitting device.

- **3.4.3** invalid: A keyword used to describe an illegal or unsupported bit, byte, word, field or code value. Receipt of an invalid bit, byte, word, field or code value shall be reported as an error.

- 3.4.4 mandatory: A keyword indicating an item that is required to be implemented as defined in this standard.

- may: A keyword that indicates flexibility of choice with no implied preference (equivalent to "may or may not")

- **3.4.6** may not: A keyword that indicates flexibility of choice with no implied preference (equivalent to "may or may not").

- 3.4.7 **obsolete**: A keyword indicating that an item was defined in prior Fibre Channel standards but has been removed from this standard.

- **3.4.8** optional: A keyword that describes features that are not required to be implemented by this standard. However, if any optional feature defined by this standard is implemented, then it shall be implemented as defined in this standard.

- **3.4.9** reserved: A keyword referring to bits, bytes, words, fields and code values that are set aside for future standardization. A reserved bit, byte, word or field shall be set to zero, or in accordance with a future extension to this standard. Recipients are not required to check reserved bits, bytes, words or fields for zero values.

- 3.4.10 restricted: A keyword referring to bits, bytes, words, and fields that are set aside for use in other Fibre Channel standards. A restricted bit, byte, word, or field shall be treated as a reserved bit, byte, word or field for the purposes of the requirements defined in this standard.

- shall: A keyword indicating a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this standard.

- 3.4.12 should: A keyword indicating flexibility of choice with a strongly preferred alternative; equivalent EC ANGS. IS to the phrase "it is strongly recommended".

- **3.4.13 x** or **xx**: The value of the bit or field is not relevant.

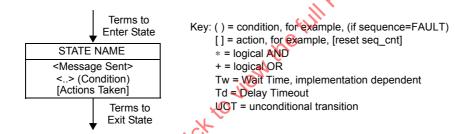

# 3.5 State Diagram notation

#### 3.5.1 State Diagram conventions

The operation of a protocol may be described by subdividing the protocol into a number of interrelated functions. The operation of the functions may be described by state diagrams. Each diagram represents the domain of a function and consists of a group of connected, mutually exclusive states. Only one state of a function is active at any given time (see figure 1).

Figure 1 - State diagram notation example

Each state that the function is able to assume is represented by a rectangle. These are divided into two parts by a horizontal line. In the upper part the state is identified by a name in capital letters. The lower part contains the name of any ON signal that is generated by the function. Actions are described by short phrases and enclosed in brackets.

All permissible transitions between the states of a function are represented graphically by arrows between them. A transition that is global in nature (e.g., an exit condition from all states to the IDLE or RESET state) is indicated by an open arrow. Labels on transitions are qualifiers that shall be fulfilled before the transition is taken. The label UCT designates an unconditional transition. Qualifiers described by short phrases are enclosed in parentheses.

State transitions and sending and receiving of messages occur instantaneously. The actions inside a state block execute instantaneously. Actions inside state blocks are atomic (i.e., uninterruptible). When a state is entered and after performing all the actions listed in a state block one time, the state block then continuously evaluates its exit conditions until one is satisfied, at which point control passes through a transition arrow to the next block. While the state awaits fulfillment of one of its exit conditions, the actions inside do not implicitly repeat.

Valid state actions may include .indication and .request messages. No actions are taken outside of any state block.

The following convention is used to describe a term-assignment statement that is associated with a transition:

- a) The character ":" (colon) is a delimiter used to denote that a term assignment statement follows; and

- b) The character "\(\infty\)" (left arrow) denotes assignment of the value following the arrow to the term preceding the arrow.

The state diagrams contain the authoritative statement of the functions they depict. When apparent conflicts between descriptive text and state diagrams arise, the state diagrams are to take precedence. However, such precedence does not override any explicit description in the text that has no parallel in the state diagrams.

The models presented by state diagrams are intended as the primary specifications of the functions to be provided. However, it is important to distinguish between a model and a real implementation. The models are optimized for simplicity and clarity of presentation, while any realistic implementation may place heavier emphasis on efficiency and suitability to a particular implementation technology. It is the functional behavior of any unit that shall match the standard, not its internal structure. The internal details of the model are useful only to the extent that they specify the external behavior clearly and precisely.

## 3.5.2 State Diagram variables

State variables are of two types, variables with no default value and variables with a default value. Variables with no default value, once set retain their value as long as succeeding blocks contain no references to them. Variables with default value evaluate to the variable default value in each state where the variable value is not explicitly set.

# 3.5.3 State Diagram timers

All timers operate in the same fashion. A timer is reset and starts counting upon entering a state where "start x\_timer" is asserted. Time "x" after the timer has been started, "x\_timer\_done" is asserted and remains asserted until the timer is reset. At all other times, "x\_timer\_not\_done" is asserted. When explicitly entering a state where "start x\_timer" is asserted, the timer is reset and restarted even if the entered state is the same as the exited state. In addition, a timer is reset and stops counting upon entering a state where "stop timer" is asserted.

# 3.5.4 State transitions

The following terms are valid transition qualifiers:

- a) Boolean expressions;

- b) An event such as the expiration of a timer: timer done;

- c) An event such as the reception of a message: PMA\_UNITDATA.indication;

- d) An unconditional transition: UCT;

e) A branch taken when other exit conditions are not satisfied: ELSE.

Any open arrow (an arrow with no source block) represents a global transition. Global transitions are evaluated continuously whenever any state is evaluating its exit conditions. When a global transition becomes true, it supersedes all other transitions, including UCT, returning control to the block pointed to by the open arrow.

# 3.5.5 Operators

The state diagram operators are shown in table 2.

Table 2 - State Diagram Operators

| s are shown in | n table 2.                                                                                                                |

|----------------|---------------------------------------------------------------------------------------------------------------------------|

| Table          | 2 – State Diagram Operators  Meaning  Boolean AND  Boolean OR  Boolean XOR  Boolean NOT  Less than  Less than or equal to |

| Character      | Meaning                                                                                                                   |

| *              | Boolean AND                                                                                                               |

| +              | Boolean OR                                                                                                                |

| ٨              | Boolean XOR                                                                                                               |

| !              | Boolean NOT                                                                                                               |

| <              | Less than                                                                                                                 |

| <b>≤</b>       | Less than or equal to                                                                                                     |

| =              | Equals (a test of equality)                                                                                               |

| <b>≠</b>       | Not equals                                                                                                                |

| ≥              | Greater than or equal to                                                                                                  |

| >              | Greater than                                                                                                              |

| ()             | Indicates precedence                                                                                                      |

| ⇐              | Assignment operator                                                                                                       |

| €              | Indicates membership                                                                                                      |

| ∉              | Indicates nonmembership                                                                                                   |

|                | Catenate                                                                                                                  |

| ELSE           | No other state condition is satisfied                                                                                     |

-LSE CO STANDARDSISO.

# 4 Structure and concepts

#### 4.1 Overview

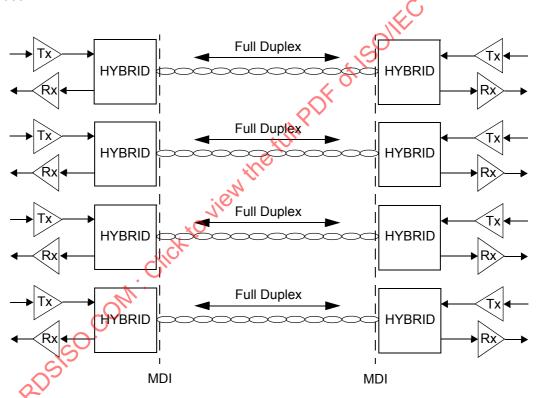

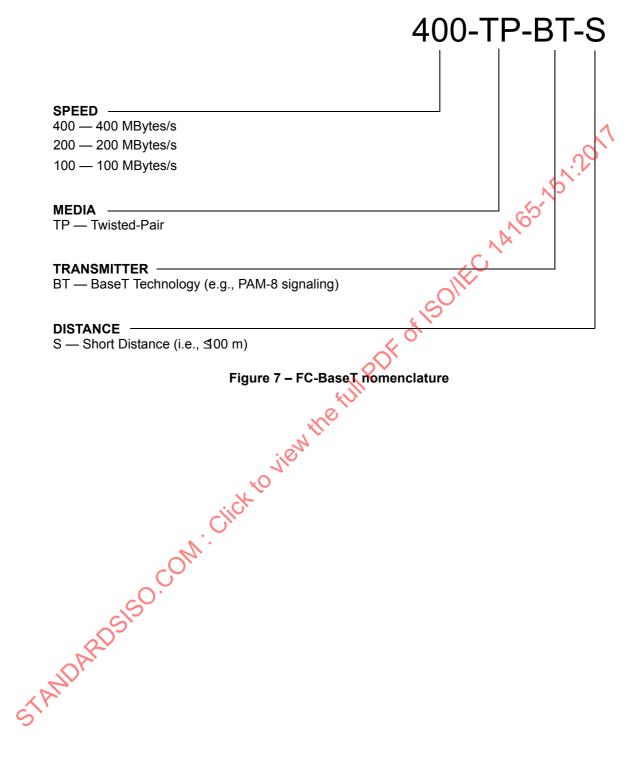

A vast infrastructure of installed twisted-pair copper cabling systems exists today. High volume has driven down the cost for copper PHYs and cabling systems to a fraction of their original cost. FC-BaseT is intended to leverage this economy of scale by permitting communication of Fibre Channel data streams at 1 Gbit/s, 2 Gbit/s, or 4 Gbit/s over balanced twisted-pair copper cabling systems.

1000BASE-T (see IEEE 802.3-2005) pioneered the use of coded multi-level baseband signaling to permit high data rates to be carried over the relatively narrow bandwidth available on balanced twisted-pair copper cabling. FC-BaseT uses a simplified version of the field proven and well understood line code of 1000BASE-T.

Twisted-pair cabling systems have limited usable bandwidth available for data transmission. FC data are de-multiplexed spatially across four physical wire pairs to reduce the data rate per wire by 75%. In addition, hybrids are employed to permit signals to be transmitted and received on the same wire pair enabling full-duplex point-to-point transmission. Figure 2 illustrates the full duplex, four wire configuration used for FC-BaseT.

Figure 2 - FC-BaseT topology

Multi-level baseband signaling (i.e, Pulse Amplitude Modulation or PAM) is used on each of the wire pairs. In a multi-level transmission scheme, multiple bits are transmitted each clock interval. Data rate (i.e., bits per second) is transformed into symbol rate (i.e., symbols per second).

The following are the objectives of FC-BaseT:

a) bit error rate (BER) better than  $10^{-12}$  (e.g.,  $\leq 10^{-15}$ );

- b) PHY delay lower than 1 μs;

- c) Meet or exceed FCC Class A/CISPR EMC requirements;

- d) Support IEEE 802.3-2005 Auto-Negotiation;

- e) Support data rates, cable types and lengths as per table 3.

Table 3 – FC-BaseT design goals for data rates and cable reaches for the cabling channels specified by ISO/IEC 11801:2002/AMD2:2010

| FC Data Rate | Class D Reach <sup>a</sup> | Class E Reach <sup>a</sup> | Class E <sub>A</sub> to F <sub>A</sub> Reach <sup>a</sup> |

|--------------|----------------------------|----------------------------|-----------------------------------------------------------|

| 1GFC-BaseT   | 100 m                      | 100 m                      | 100 m                                                     |

| 2GFC-BaseT   | 60 m                       | 70 m                       | 100 m                                                     |

| 4GFC-BaseT   | 30 m <sup>b</sup>          | 40 m                       | 100 m                                                     |

<sup>&</sup>lt;sup>a</sup> Similar channels up to Class E<sub>A</sub> are specified in TIA/EIA standards as Category 5e, Category 6 and Category 6a (see Annex D).

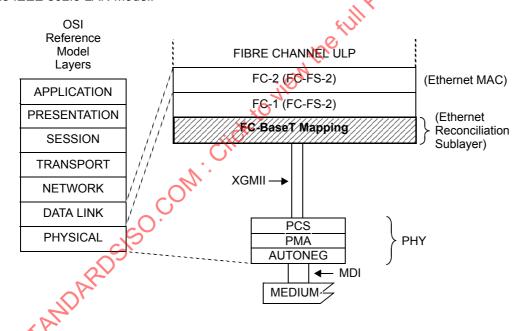

# 4.2 Relationship with other standards

Figure 3 shows the model of the FC-BaseT FC-0 level, and its relationship with the ISO Reference model and the IEEE 802.3 LAN Model.

MAC = MEDIA ACCESS CONTROL

MDI = MEDIUM DEPENDENT INTERFACE

PHY = PHYSICAL LAYER DEVICE

PCS = PHYSICAL CODING SUBLAYER

PMA = PHYSICAL MEDIUM ATTACHMENT

AUTONEG = AUTONEGOTIATION

XGMII = 10 GIGABIT MEDIA INDEPENDENT INTERFACE (optional)

Figure 3 – FC-BaseT relationship to the OSI Reference Model, the Fibre Channel Levels, and the IEEE 802.3 LAN Model

b Expected performance, not guaranteed. 4GFC-BaseT exceeds the rated frequency performance of Class D channels (see ISO/IEC TR 24750).

An optional XGMII interface is used in this specification because it allows an easy representation of Fibre Channel data characters and control codes. Implementations are not required to expose nor use this interface. The XGMII interface is used in this standard as specified in 4.4.

#### 4.3 FC-BaseT PHY logical model

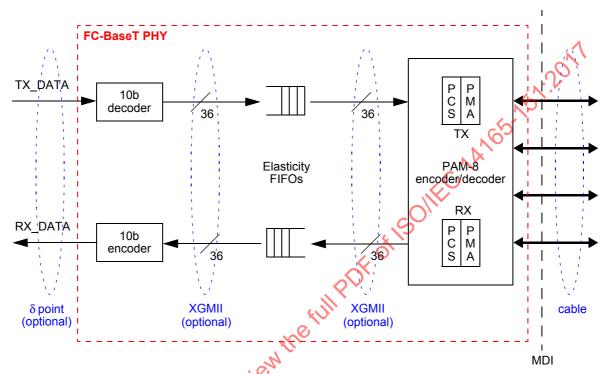

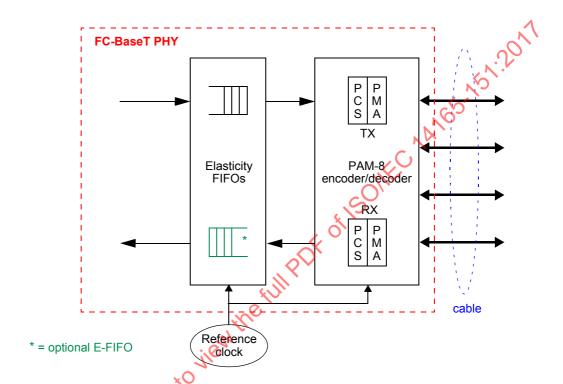

The logical model of a possible FC-BaseT PHY implementation is shown in figure 4.

Figure 4 - An FC-BaseT PHY logical model

Fibre Channel is a full duplex continuously transmitting technology (i.e., when no data are to be sent, Idles and other Ordered Sets are transmitted by the upper layers). An FC-BaseT PHY transmits on the cable a continuous stream of data coming from the upper layers and receives a continuous stream of data from the cable. A Fibre Channel data stream is composed of frames and Ordered Sets. In some cases (e.g., when the particular Fibre Channel logical topology is an Arbitrated Loop, see FC-AL-2) Ordered Sets are used continuously in an information stream.

An FC-BaseT RHY may use the same electrical interface specified for the  $\delta$  points (see FC-PI-2) for the various Fibre Channel speeds. In this case, on entering the FC-BaseT PHY the 10b encoding of the FC serial stream is removed and the FC data are converted in an internal stream of 36-bit XGMII words, as shown in figure 4.

The Elasticity FIFOs resolve potential clock skews between two connected PHYs and retime the data stream to be compliant with the FC-PI-2 jitter specification.

The PAM-8 encoder/decoder converts each 36-bit word on the XGMII interface in three 4-dimensional (4D) PAM-8 symbols. Each 4D symbol is a 4-tuple ( $A_n$ ,  $B_n$ ,  $C_n$ ,  $D_n$ ) of 1-dimensional signals, each taken from the set {-7, -5, -3, -1, +1, +3, +5, +7}. Each 4D symbol is sent as an 8-level pulse amplitude modulated signal on each of the four wire pairs, called Bl\_DA, Bl\_DB, Bl\_DC, and Bl\_DD.

This standard defines the FC-BaseT γ point (see FC-PI-2) at the MDI, and does not specify requirements for the host to PHY interface. Implementation of  $\delta$  points is optional (e.g., a PHY may implement a different host to PHY interface, or the PHY may be integrated in a protocol ASIC). When an FC-BaseT PHY is integrated in a protocol ASIC, it may be coupled directly with the FC-1 level. System operation from the perspective of signals at the MDI and management objects shall be independent from the host to PHY interface.

# 4.4 FC-BaseT usage of XGMII

The XGMII interface is defined in IEEE 802.3-2005 to support 10 Gbit/s operations, but is used in this standard to support the Fibre Channel speeds of 4 Gbit/s, 2 Gbit/s, and 1 Gbit/s with the clock frequencies EC 14165-151.201 shown in table 4.

|            | •               |

|------------|-----------------|

| FC Speed   | XGMII Frequency |

| 4GFC-BaseT | 53,125 MHz      |

| 2GFC-BaseT | 26,562 5 MHz    |

| 1GFC-BaseT | 13,281 25 MHz   |

Table 4 - XGMII frequencies for FC-BaseT

XGMII is a 36-bit interface carrying four characters at a time. Each character is represented as eight data bits (called TXD in the transmit direction, RXD in the receive direction) and one control bit (called TXC in the transmit direction, RXC in the receive direction). The XGMII characters are summarized in table 5.

|              | Table         | 5 – XGMII charac | cters |

|--------------|---------------|------------------|-------|

| GMII TXC/RXC | XGMII TXD/RXD | 10b Character    |       |

|              |               |                  |       |

| XGMII TXC/RXC | XGMII TXD/RXD | 10b Character | Description                     |

|---------------|---------------|---------------|---------------------------------|

| 0b            | 00h FFh       | Dxx.y         | Data characters                 |

| 1b            | 07h           | _a            | XGMII Idle character (/I/)      |

| 1b            | 1Ch           | K28:0         | Reserved XGMII character        |

| 1b            | 3Ch           | K28.1         | Reserved XGMII character        |

| 1b            | 5Ch           | K28.2         | Primitive XGMII character (/P/) |

| 1b            | 7Ch           | K28.3         | Reserved XGMII character        |

| 1b            | 9Ch           | K28.4         | Sequence XGMII character (/Q/)  |

| 1b            | BCh           | K28.5         | Reserved XGMII character        |

| 1b            | DCh           | K28.6         | Reserved XGMII character        |

| 1b            | F7h           | K23.7         | Reserved XGMII character        |

| 1b            | FBh           | K27.7         | Start XGMII character (/S/)     |

| 1b            | FCh           | K28.7         | Reserved XGMII character        |

| 1b            | FDh           | K29.7         | Terminate XGMII character (/T/) |

| 16            | FEh           | K30.7         | Error XGMII character (/E/)     |

| 1b            | all others    | K30.7         | Invalid XGMII character (/E/)   |

<sup>&</sup>lt;sup>a</sup> The XGMII Idle character, denoted as K07, does not have a 10b representation. IEEE 802.3-2005, clause 36.2.4.12, defines how to encode the K07 character for transmission in a 10b encoded serial stream.

# 4.5 Operation of FC-BaseT

#### 4.5.1 Overview

FC-BaseT employs full duplex baseband transmission over four pairs of balanced cabling. The aggregate data rate is achieved by transmitting in each direction simultaneously on each wire pair, as shown in figure 2. Baseband 8-level PAM signaling is used on each of the wire pairs. Transmitted levels on each wire pair are selected from a 4-dimensional 8-level signal constellation. Each 4-dimensional symbol is a 4-tuple ( $A_n$ ,  $B_n$ ,  $C_n$ ,  $D_n$ ) of 1-dimensional signals, each taken from the set {-7, -5, -3, -1, +1, +3, +5, +7}. This modulation scheme is called 4D PAM-8. The FC-BaseT data rate, symbol rate and symbol period per each of the supported FC-BaseT speeds is shown in table 6.

| FC Speed   | FC0 Data Rate  | FC-BaseT<br>Data Rate | FC-BaseT Symbol<br>Rate per Wire | Symbol Period           |

|------------|----------------|-----------------------|----------------------------------|-------------------------|

| 4GFC-BaseT | 4,25 Gbit/s    | 3,4 Gbit/s            | 318,75 Ms/s                      | ~3,137 ns <sup>a</sup>  |

| 2GFC-BaseT | 2,125 Gbit/s   | 1,7 Gbit/s            | 159,375 Ms/s                     | ~6,274 ns <sup>b</sup>  |

| 1GFC-BaseT | 1,062 5 Gbit/s | 0,85 Gbit/s           | 79,687 5 Ms/s                    | ~12,549 ns <sup>C</sup> |

The exact symbol period is 160/51 ns.

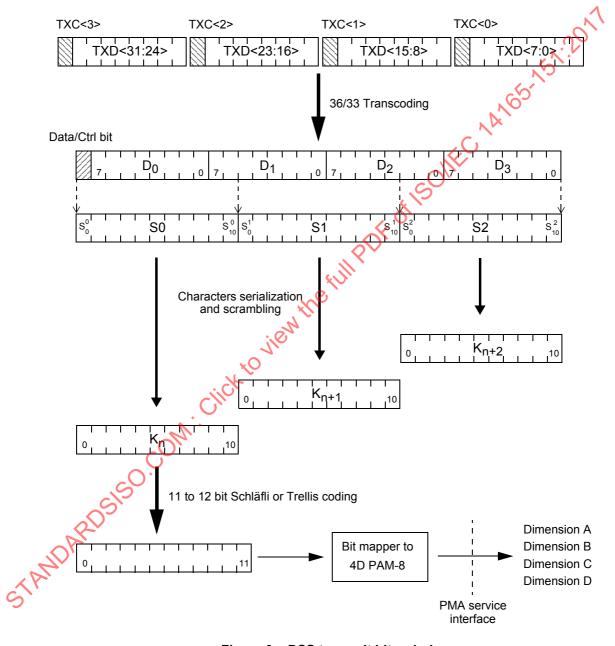

Data and control characters are encoded at a rate of 2,75 information bits per PAM-8 symbol. Data and control characters are embedded in a framing scheme that runs continuously after startup of the link. PHY blocks consisting of three 4D PAM-8 symbols are continuously transmitted after link startup.

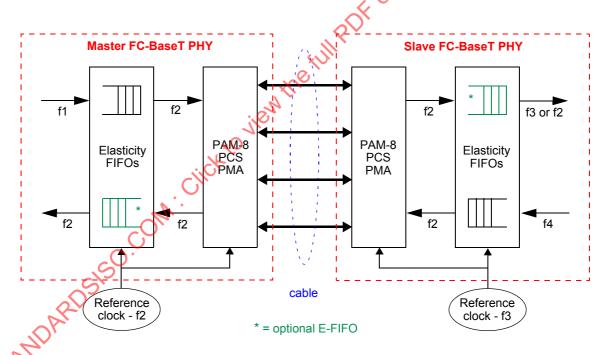

An FC-BaseT PHY may operate either as a Master PHY or as a Slave PHY. The Master-Slave relationship between two stations sharing a link segment is established during Auto-Negotiation (see 8.4). The Master PHY uses a local clock to determine the timing of transmitter operations. The Slave PHY recovers the clock from the received signal and uses it to determine the timing of transmitter operations (i.e., it performs loop timing).

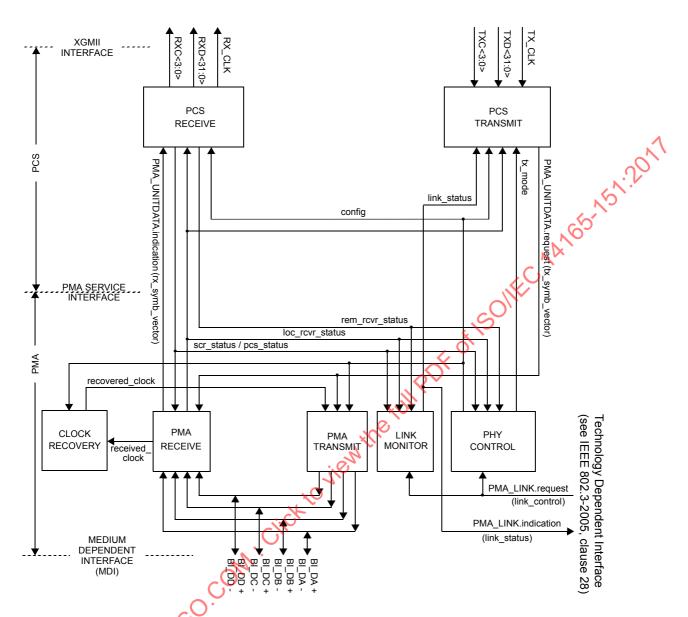

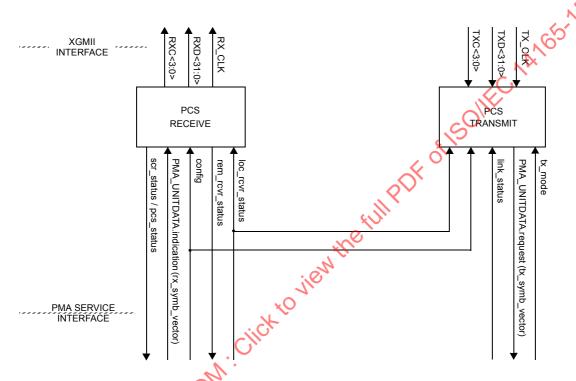

An FC-BaseT PHY may be functionally decomposed in a Physical Coding Sublayer (PCS) and a Physical Medium Attachment (PMA) sublayer, summarized respectively in 4.5.2 and 4.5.3. Figure 5 shows the functional block diagram of the PCS and PMA sublayers.

All FC-BaseT PHY implementations shall be compatible at the MDI (see figure 4). Designers are free to implement circuity within the PCS and PMA in an application-dependent manner provided that the MDI specification is met. Physical implementation of the XGMII is optional. System operation from the

b The exact symbol period is 320/51 ns.

<sup>&</sup>lt;sup>c</sup> The exact symbol period is 640/51 ns.

perspective of signals at the MDI and management objects are identical whether the XGMII is implemented or not.

Figure 5 – PCS and PMA functional block diagram

# 4.5.2 PCS overview

The FC-BaseT Physical Coding Sublayer (PCS) couples the XGMII to the FC-BaseT Physical Medium Attachment (PMA) sublayer. The PCS supports a normal mode of operation and a training mode. Furthermore, the PCS contains a management interface.

In the transmit direction, in normal mode (see 5.3), the PCS transcodes each 36-bit XGMII word in a 33-bit block. Each 33-bit block is divided into three 11-bit transmission characters that are individually scrambled. Each 11-bit scrambled transmission character is then either Schläfli lattice or Trellis encoded in 12 bits (see 5.3.5 and 5.3.6). The defined Schläfli lattice coding defined in 5.3.5 is a proper subset of the Trellis coding defined in 5.3.6. The encoding to be used by the local PHY is dictated by the link partner PHY during

Auto-Negotiation. The 12 bits obtained after encoding are in turn divided in four groups of three bits, each identifying a symbol in the PAM-8 symbol set {-7, -5, -3, -1, +1, +3, +5, +7}. The obtained 4D PAM-8 symbols are passed on to the PMA as a PMA\_UNITDATA.request primitive.

In the receive direction, in normal mode (see 5.4), the PCS processes code-groups received from the remote PHY via the PMA and maps them to the XGMII service interface in the receive path. In this receive processing scheme, symbol clock synchronization is done by the PMA receive function.

#### 4.5.3 PMA overview

The PMA sublayer couples messages from the PMA service interface onto the balanced cabling physical medium and provides the link management and PHY Control functions. The PMA provides full duplex communications over four pairs of balanced cabling.

The PMA Transmit function (see 6.2.2) comprises four independent transmitters to generate PAM-8 signals on each of the four pairs BI\_DA, BI\_DB, BI\_DC, and BI\_DD.

The PMA Receive function (see 6.2.3) comprises four independent receivers for PAM-8 signals on each of the four pairs BI\_DA, BI\_DB, BI\_DC and BI\_DD. The receivers are responsible for acquiring symbol timing and, when operating in normal mode, for cancelling echo, near-end crosstalk, far-end crosstalk, and equalizing the signal. The 4D PAM-8 symbols are provided to the PCS receive function via the PMA UNITDATA.indication primitive. The PMA also contains functions for Link Monitor.

The PHY Control function (see 6.2.4) generates signals that control the PCS and PMA sublayer operations. PHY Control begins following the completion of Auto-Negotiation and provides the start-up functions required for successful FC-BaseT operation. It determines whether the PHY operates in normal mode, enabling data transmission over the link segment, or whether the PHY sends special PAM-2 code-groups that are used in training mode.

# 4.6 FC-BaseT service primitives and interfaces

# 4.6.1 Overview

FC-BaseT transfers data and control information across the following four service interfaces:

- a) XGMII Service Interface (see 4.4);

- b) PMA Service Interface (see 4.6.2);

- c) Medium Dependent Interface (see 6.4); and

- d) Management Function Interface (see 4.6.3).

# 4.6.2 PMA service interface

#### 4.6.2.1 Overview

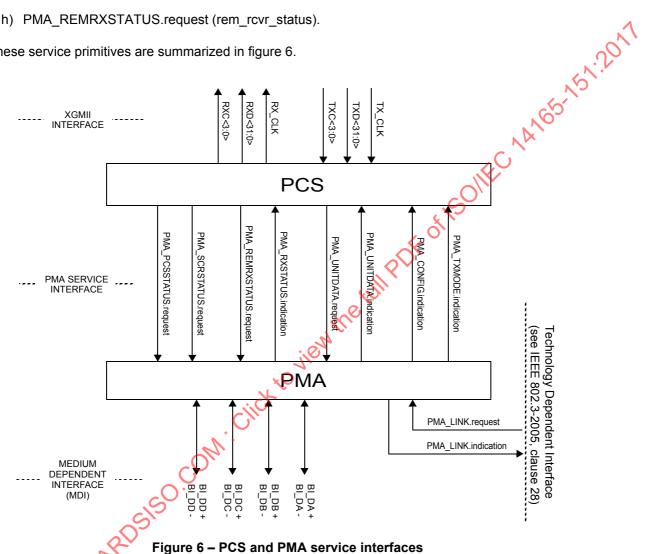

FC-BaseT uses the following service primitives to exchange symbol vectors, status indications, and control signals across the PMA service interface:

- a) PMA\_TXMODE.indication (tx\_mode);

- b) PMA\_CONFIG.indication (config);

- c) PMA\_UNITDATA.request (tx\_symb\_vector);

- d) PMA\_UNITDATA.indication (rx\_symb\_vector);

- PMA\_SCRSTATUS.request (scr\_status);

- PMA\_PCSSTATUS.request (pcs\_status); f)

- PMA\_RXSTATUS.indication (loc\_rcvr\_status); and

- h) PMA\_REMRXSTATUS.request (rem\_rcvr\_status).

These service primitives are summarized in figure 6.

# 4.6.2.2 PMA\_TXMODE.indication

Semantics of the primitive: PMA TXMODE.indication (tx mode)

This primitive specifies to PCS Transmit via the parameter tx\_mode what sequence of code-groups the PCS should be transmitting.

The parameter tx\_mode may assume one of the following values:

- a) SEND Z: This value is continuously asserted when the transmitters are required to be silent;

- b) SEND\_T1: This value is continuously asserted when transmission of sequences of 4D Type-1 PAM-2 symbols representing the training mode is to take place;

- c) SEND\_T2: This value is continuously asserted when transmission of sequences of 4D Type-2 PAM-2 symbols representing the trained mode is to take place;

- d) SEND\_I2: This value is continuously asserted when transmission of sequences of 4D PAM-8 symbols representing the scrambled Idle2 Ordered Set is to take place;

- e) SEND\_I3: This value is continuously asserted when transmission of sequences of 4D PAM-8 symbols representing the scrambled Idle3 Ordered Set is to take place; or

- f) SEND\_N: This value is continuously asserted when transmission of 4D PAM-8 symbols representing scrambled XGMII words or scrambled Idle3 Ordered Sets in normal mode is to take place.

**When generated:** The PHY Control function generates PMA\_TXMODE.indication messages to indicate a change in tx mode.

Effect of receipt: Upon receipt of this primitive, the PCS performs its Transmit function (see 5.3).

## 4.6.2.3 PMA CONFIG.indication

Semantics of the primitive: PMA\_CONFIG.indication (config)

This primitive specifies to the PCS and PMA Transmit functions via the parameter config whether the PHY operates as a Master PHY or as a Slave PHY. The Master-Slave configuration is determined during Auto-Negotiation.

The parameter config may assume one of the following values:

- a) MASTER: This value is continuously asserted when the PHY operates as a Master PHY; or

- b) SLAVE: This value is continuously asserted when the PHY operates as a Slave PHY.

When generated: The PMA generates PMA\_CONFIG.indication messages to indicate a change in config.

**Effect of receipt:** PCS and PMA Clock Recovery perform their functions in Master or Slave configuration according to the value assumed by the parameter config.

# 4.6.2.4 PMA\_UNITDATA.request

**Semantics of the primitive:** PMA UNITDATA.request (tx symb vector)

This primitive defines the transfer of code-groups in the form of the tx\_symb\_vector parameter from the PCS to the PMA. The code-groups are obtained in the PCS Transmit function using the encoding rules defined in 5.3 to represent XGMII data and control streams or other sequences. The PMA\_UNITDATA.request simultaneously conveys to the PMA via the parameter tx\_symb\_vector the value of the symbols to be sent over each of the four transmit pairs BI\_DA, BI\_DB, BI\_DC, and BI\_DD.

The tx symb vector parameter takes on the form:

a) SYMB\_4D: A vector of four multi-level symbols, one for each of the four transmit pairs BI\_DA, BI\_DB, BI\_DC, and BI\_DD. Each symbol may assume one of the values in the set {-7, -5, -3, -1, +1, +3, +5, +7}.

The symbols that are elements of tx\_symb\_vector are called, according to the pair on which each is transmitted, tx\_symb\_vector[BI\_DA], tx\_symb\_vector[BI\_DB], tx\_symb\_vector[BI\_DC], and tx\_symb\_vector[BI\_DD].

**When generated:** The PCS generates PMA\_UNITDATA.request (SYMB\_4D) synchronously with every transmit clock cycle.

**Effect of receipt:** Upon receipt of this primitive the PMA transmits on the MDI the signals corresponding to the indicated symbols. The parameter tx\_symb\_vector is also used by the PMA Receive function to process the signals received on pairs BI\_DA, BI\_DB, BI\_DC, and BI\_DD for cancelling the echo and near end crosstalk (NEXT).

# 4.6.2.5 PMA\_UNITDATA.indication

Semantics of the primitive: PMA\_UNITDATA.indication (rx\_symb\_vector)

This primitive defines the transfer of code-groups in the form of the rx\_symb\_vector parameter from the PMA to the PCS. The PMA\_UNITDATA.indication simultaneously conveys to the PCS via the parameter rx\_symb\_vector the values of the symbols detected on each of the four receive pairs BI\_DA, BI\_DB, BI\_DC, and BI\_DD.

The rx symb vector parameter takes on the form:

a) SYMB\_4D: A vector of four multi-level symbols that is the receiver's best estimate of the symbols that were sent by the remote transmitter across the four pairs. Each symbol may assume one of the values in the set {-7, -5, -3, -1, +1, +3, +5, +7}.

The symbols that are elements of rx\_symb\_vector are called, according to the pair upon which each symbol is received, rx\_symbol\_vector[BI\_DA], rx\_symbol\_vector[BI\_DB], rx\_symbol\_vector[BI\_DC], and rx\_symb\_vector[BI\_DD].

When generated: The PMA generates PMA\_UNITDATA.indication (SYMB\_4D) messages synchronously with signals received at the MDI. The nominal rate of the PMA\_UNITDATA.indication primitive is governed by the recovered clock.

**Effect of receipt:** The effect of receipt of this primitive is specified in 5.4.1.

# 4.6.2.6 PMA\_SCRSTATUS request

**Semantics of the primitive:** PMA\_SCRSTATUS.request (scr\_status)

This primitive is generated by PCS Receive to communicate the status of the descrambler for the local PHY. The parameter ser\_status conveys to the PMA Receive and PHY Control functions the information that the descrambler has achieved synchronization.

The scr status parameter may assume one of the following values:

- a) OK: The descrambler has achieved synchronization; or

- b) NOT OK: The descrambler is not synchronized.

**When generated:** PCS Receive generates PMA\_SCRSTATUS.request messages to indicate a change in scr\_status.

Effect of receipt: The effect of receipt of this primitive is specified in 6.2.3 and 6.2.4.

# 4.6.2.7 PMA\_PCSSTATUS.request

**Semantics of the primitive:** PMA\_PCSSTATUS.request (pcs\_status)

This primitive is generated by PCS Receive to indicate the fully operational state of the PCS for the local PHY. The parameter pcs\_status conveys to the PMA Receive, PHY Control and Link Monitor functions the information that the PCS is operating reliably in data mode.

The pcs\_status parameter may assume one of the following values:

- a) OK: The PCS is operating reliably in data mode; or

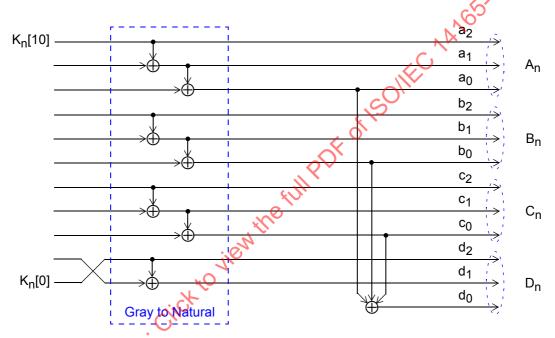

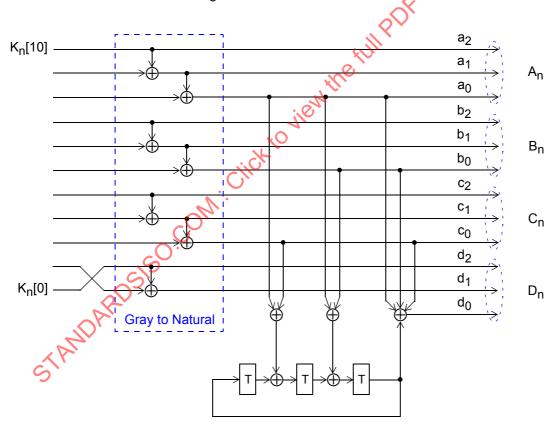

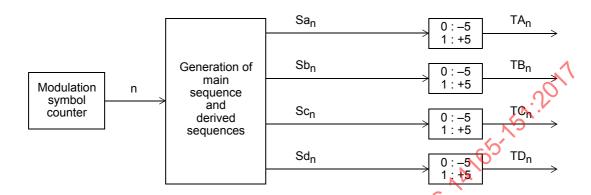

- b) NOT\_OK: The PCS is not operating reliably in data mode.